Hello

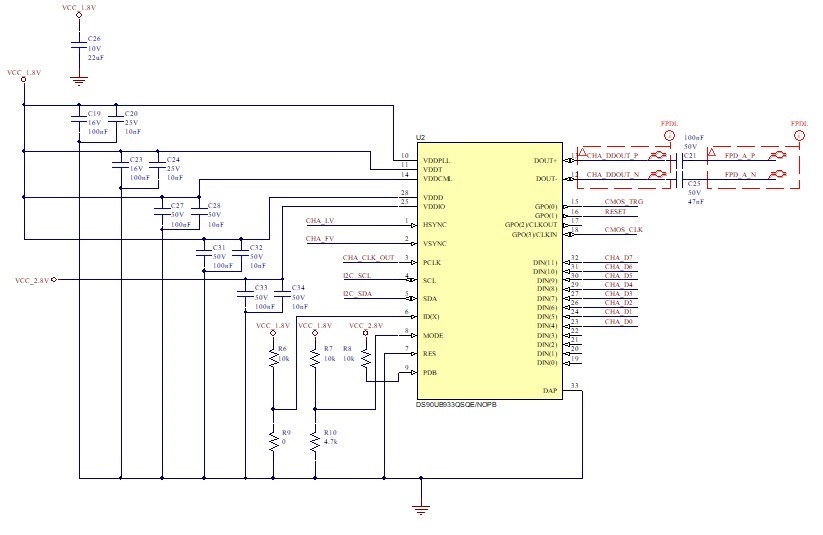

we are debuggin a new project pcb board based on FPDLINK 933 and 934. We are facing some issues in communication.

- 933 side the OnSemi ar0239 and mt9p031 cmos sensor (at 48MHz)

- 934 side a Xilnx FPGA

- using STP cable without POC

- 933 configured to use PIXCLK source from sensor (reg 0x3 set to 0xc3)

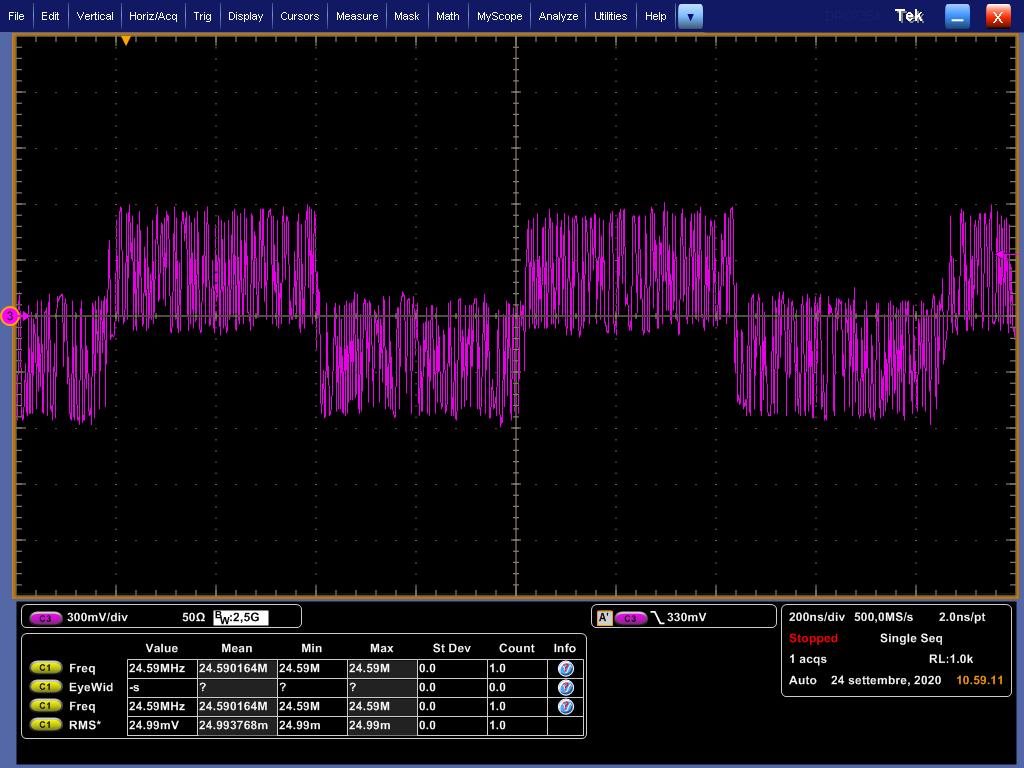

What we see is that sometimes PASS signal goes down for about 2-5 cycles of clock (and of course the stream "jump" with strange image effects). LOCK remains stable. We guess that something is going wrong in the communication path. We start to investigate the signals, and the signal at receiver side is strange. It seems modulated with a frequency of about 1.2MHz, that changes if we change the cable lenght. I attach a screenshot.

What could be the issues? Could someone help us to find what is going on?

Thanks