Other Parts Discussed in Thread: AM3352

Hi,

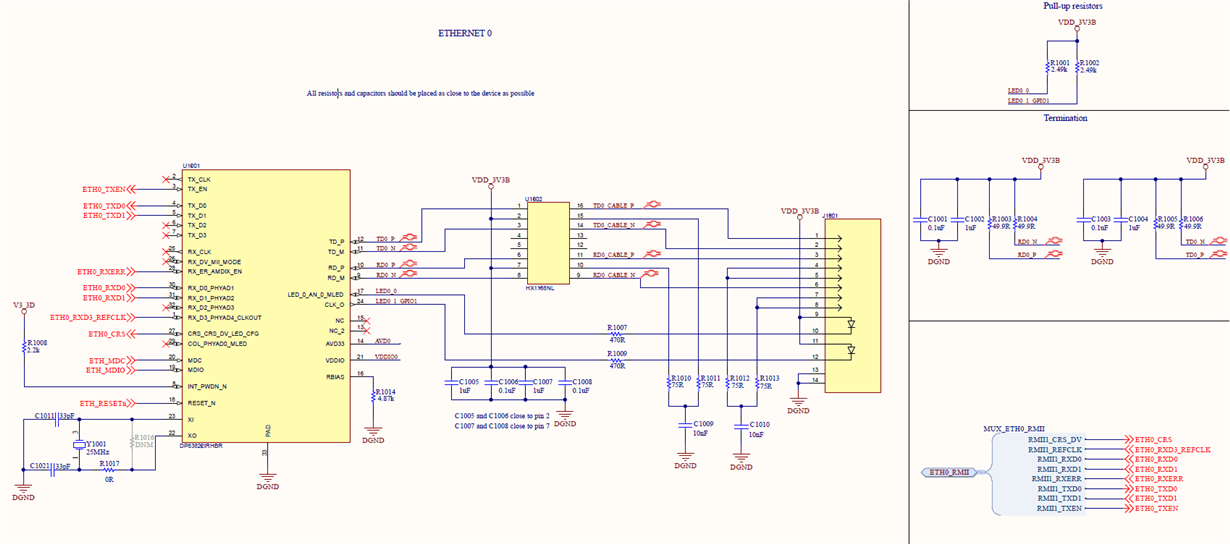

I use AM3352 along with DP83822I on my custom board.

I have a problem with the correct PHY configuration in RMII mode (master mode).

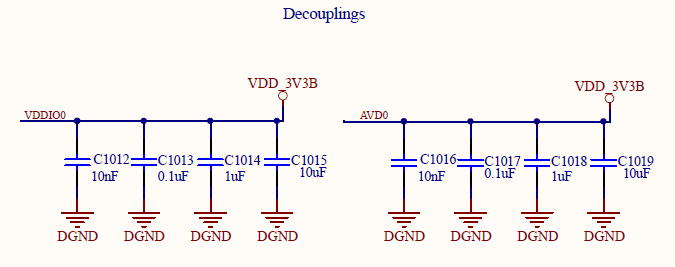

The interface connection and bootstrap configuration are as bellow.

According to this bootstrap configuration, the PHY starts in MII and I use U-boot along with MDIO to write proper values to PHY registers.

I found that I have to write:

0x61 into register 0x17

0x4300 into register 0x462

The sequence is as follows:

mii write 1 0D 1F mii write 1 0E 462 mii write 1 0D 401F mii write 1 0E 4300 mii write 1 17 61

The link status and auto-negotiation act properly.

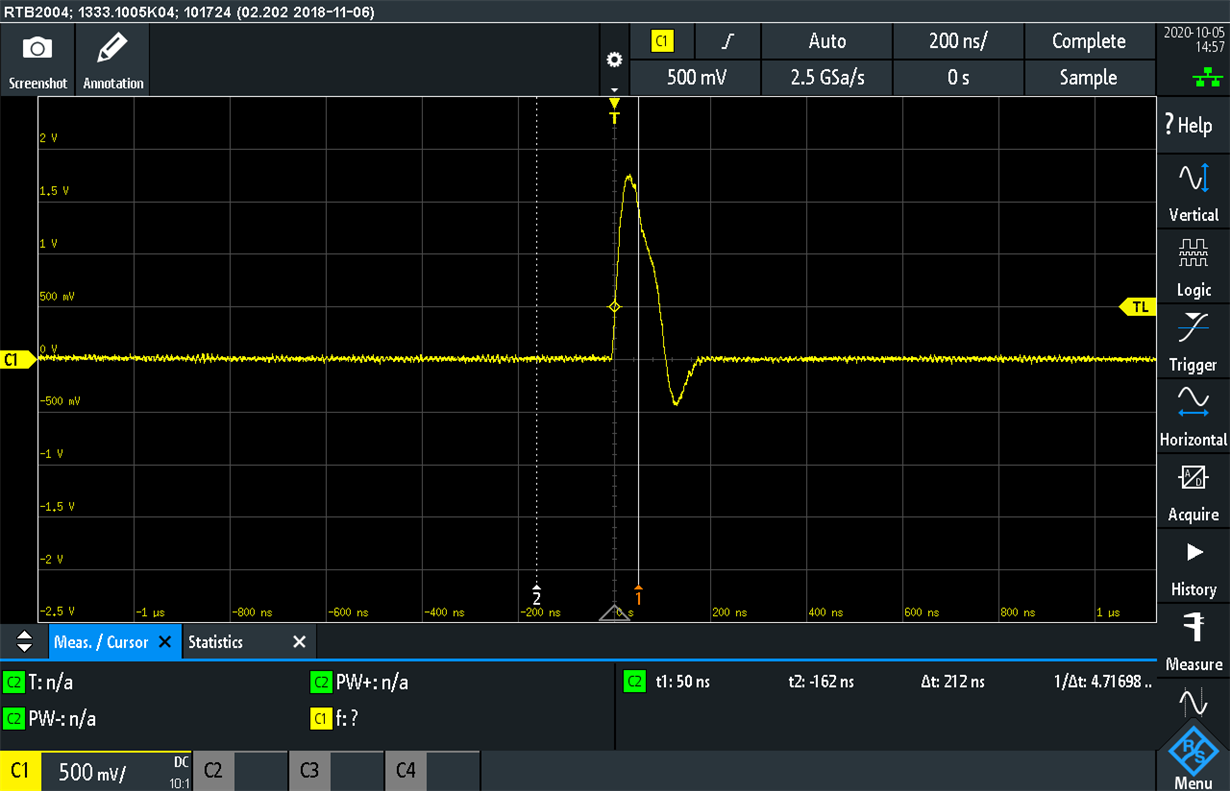

However, I'm not able to send anything and I see overflow detected.

I see big numbers in registers FCSCR and RECR.

Questions:

1) Which registers do I need to configure? (assuming the bootstrap is configured as shown above). Have I missed anything I need to change?

2) How can I find out what is wrong in my configuration?

3) What are the recommended steps to troubleshoot this issue?