Hi TI support team

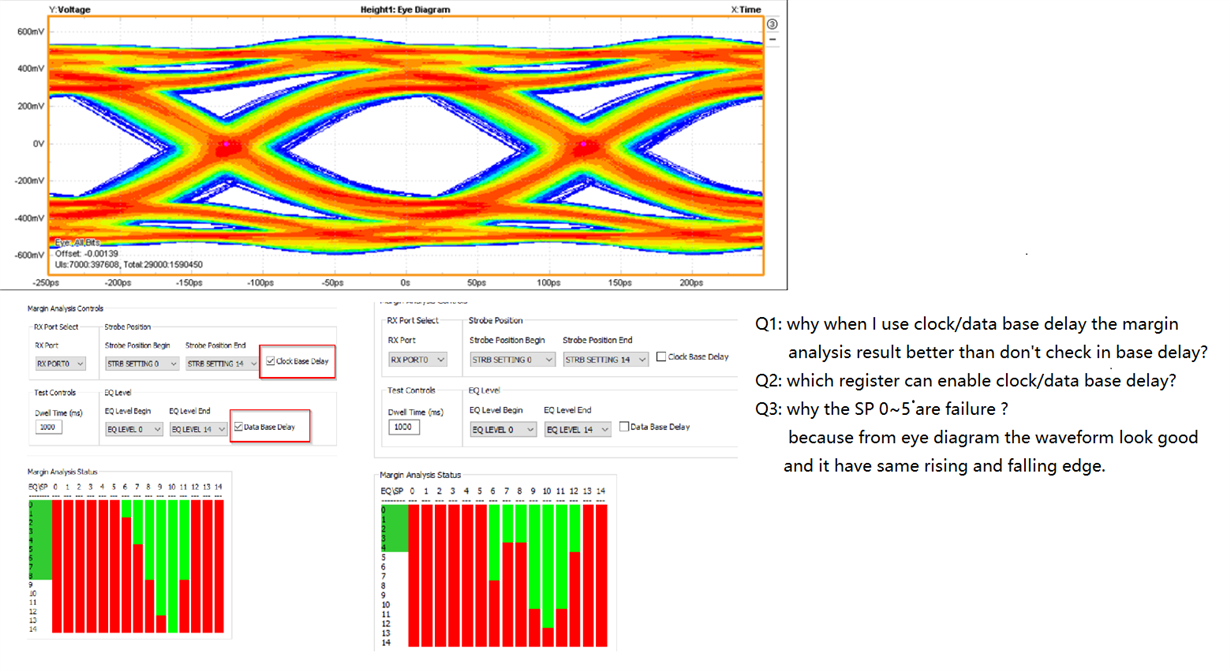

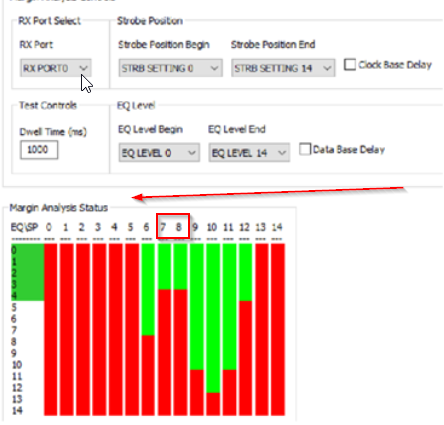

Some question about the DS90UB954 MAP margin analysis result, you can find the drawing in below.

Please give your comments.

Q1: why when I use clock/data base delay the margin analysis result better than don't check in base delay?

Q2: which register can enable clock/data base delay?

Q3: why the SP 0~5 are failure ? because I have test the CMLOUT eye diagram the waveform look good and it have same rising and falling edge. but I have confuse about your margin analysis result.

Thanks

Yutai