Other Parts Discussed in Thread: DS32EL0124

Hello,

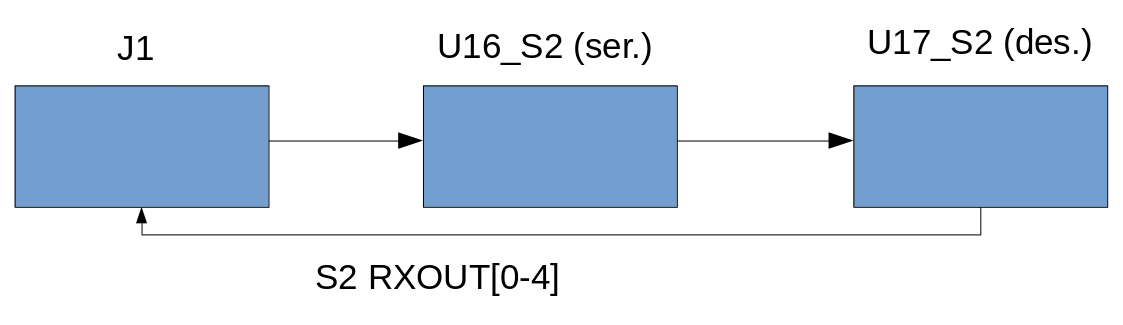

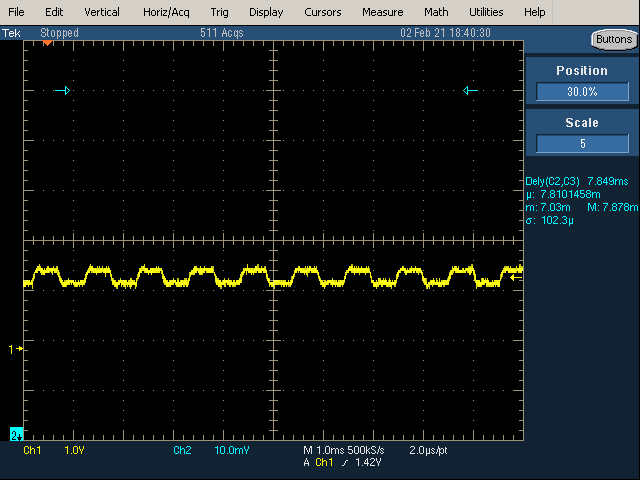

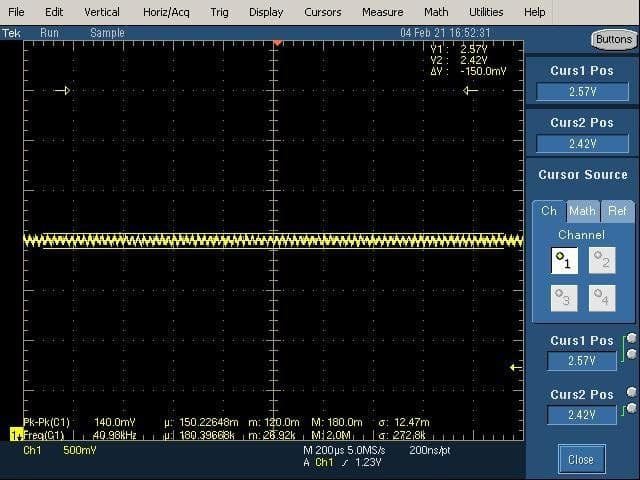

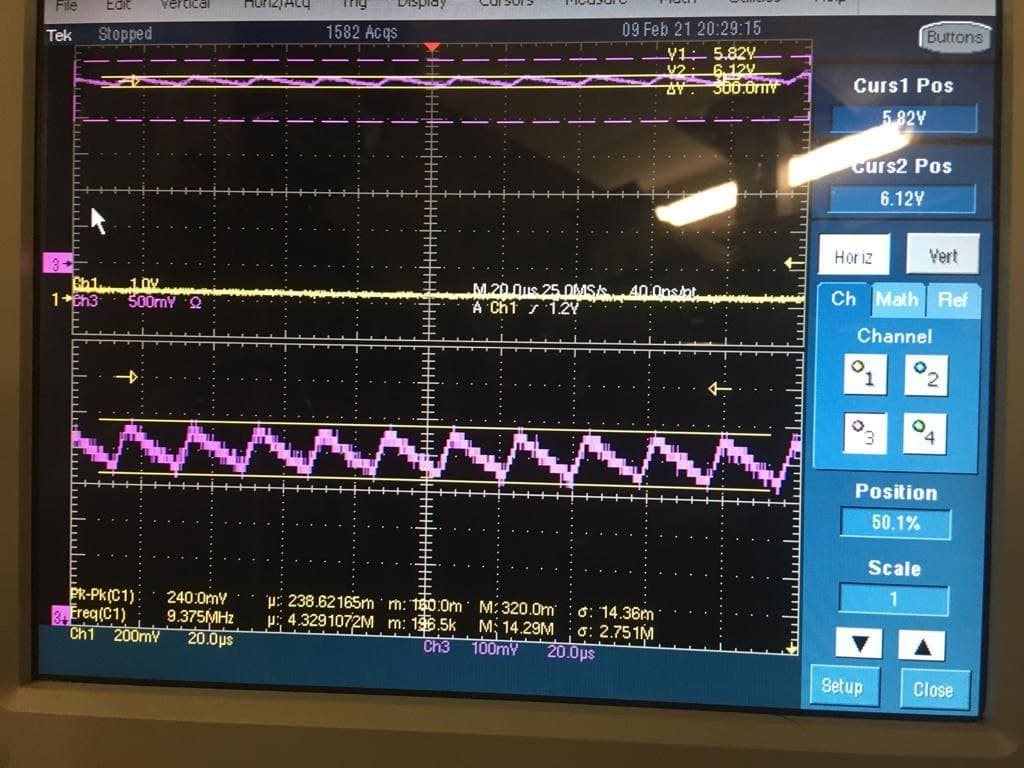

We have designed a custom PCB board featuring a serializer (DS32EL0421) and a deserializer (DS32EL0124). We send a 160 MHz clock to the serializer chip, which however does not seem to lock onto it (the "not lock" pin is at "1"). We use the configuration with remote sense and DC balance enabled.

Please find attached the schematic of the board. Note that in order to test the board we connected the serializer output to the deserializer input. Do you spot any flaw in the design?

Thank you for your attention

Kind regards,

Pietro Carra