Other Parts Discussed in Thread: TPS54561

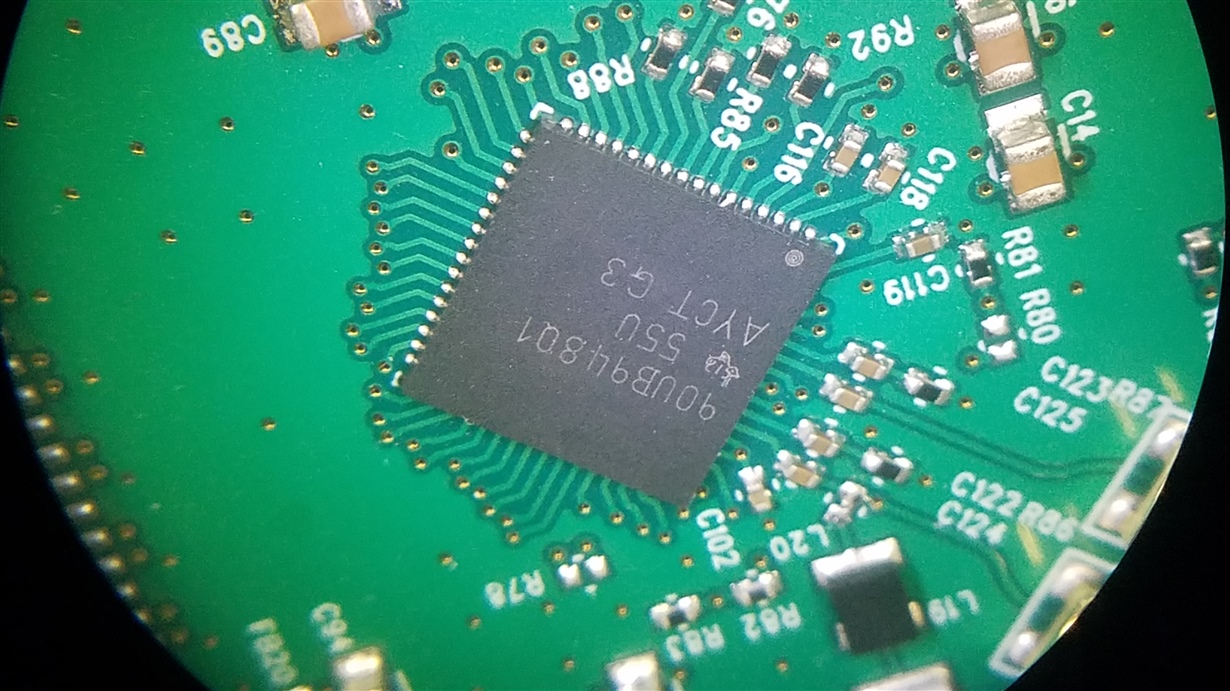

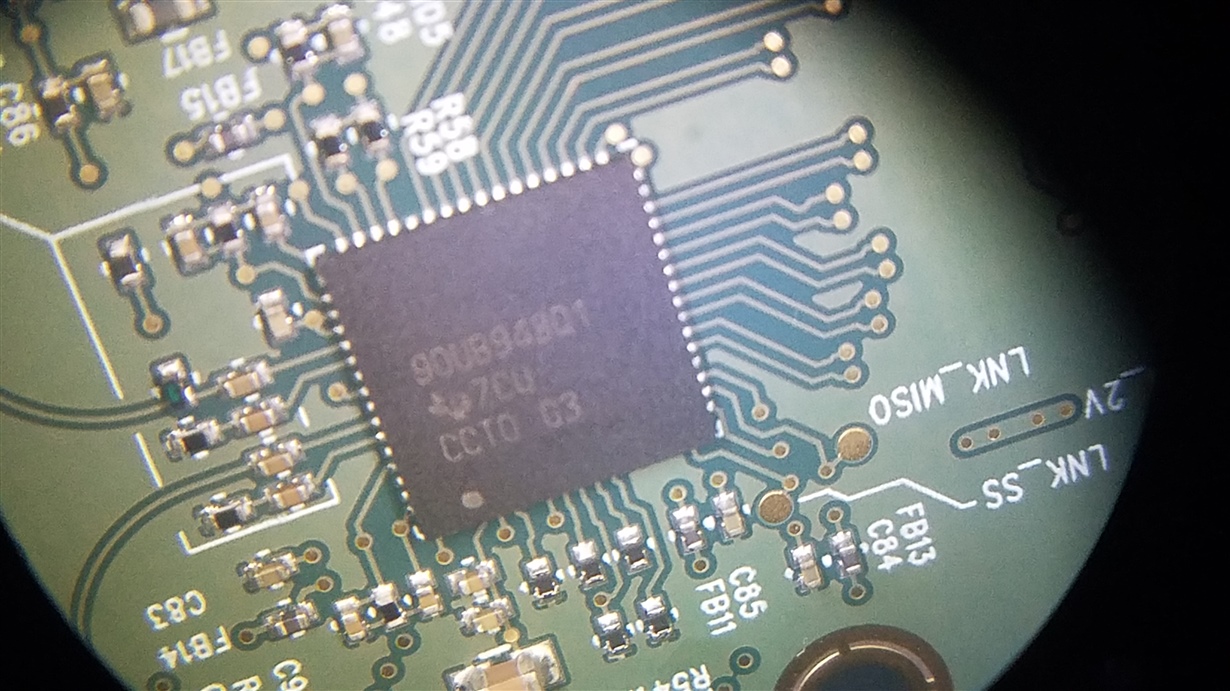

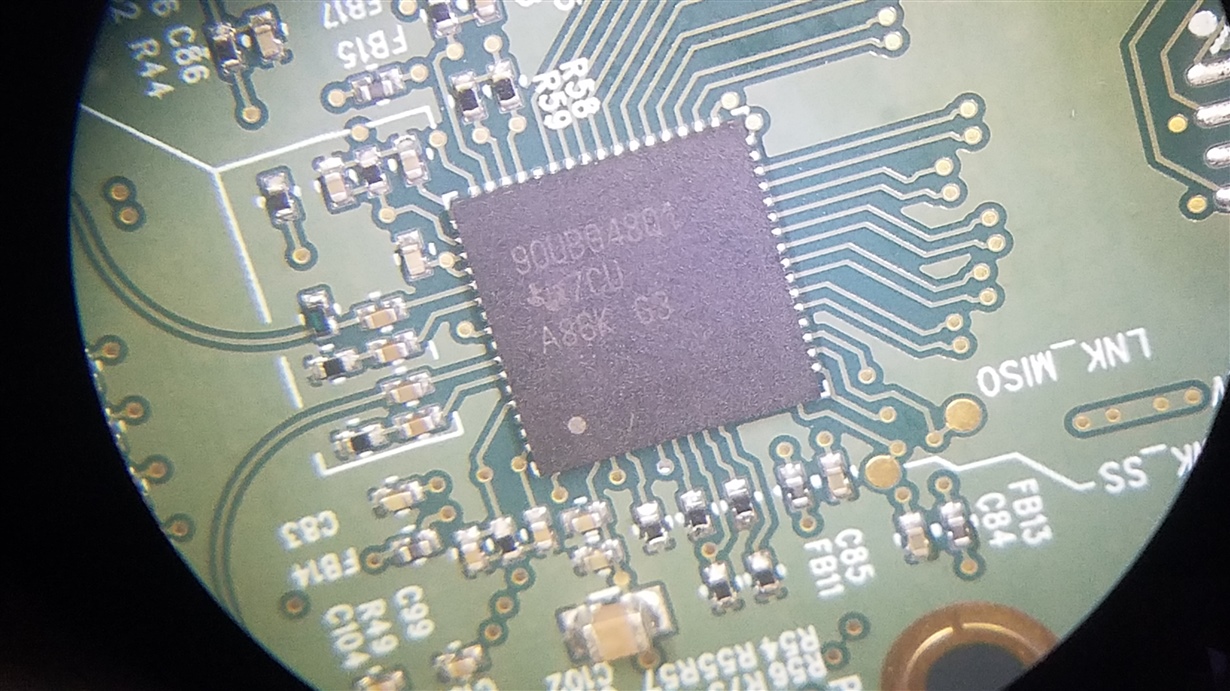

Background: We have a successful pair of boards using 947/948's. Now, we spun the 948 deserializer card to migrate from an ARM M3 to a newer M4. We also changed the connector to a D-Sub coax. The previous version was also coax. But, it used a MIL style coax in a circular connector. We don't think our current issue is the connector. Just want to mention all differences, just in case. While generating the schematics, I literally copied most circuits surrounding the 948 and pasted them into the new design. But, it is a new layout. We are testing with known good 947 serializer cards that work fine with the previous ARM M3 design. We also have EVM cards.

Issue: We are seeing a large number, as many as 65000 in a few minutes, back channel CRC errors. Resorting to verifying the link using BIST, we seem to see fewer, typically 20 to 100 in 10 seconds to 60 seconds of BIST. We suspect those may be CRC errors just prior or after BIST while we're reading the registers. Since, far end registers are unavailable during BIST (so it seems). We don't see forward channel (BIST) errors very often. But, they do occasionally show up in BIST. We have tried various cable lengths. My current test rig has been shortened down to 18" of coax.

The 948 chips in this batch on the newly developed card are much newer than previous batches. We also noticed the data sheet has had some changes since 2014, the one we used for the original design. Latest is Nov 2018. The new datasheet is better. But, nothing really new that we didn't already learn, sometimes the hard way, jumped out at us.

Questions: Is there any chance new 948 devices might have issues working with old 947 date code parts? Or, is there a new or changed register setting we should know about? (I have to ask.)

Do you have suggestions how to further analyze or diagnose this issue?

Thanks,

Howard