Other Parts Discussed in Thread: DS90UB954-Q1

Hi TI

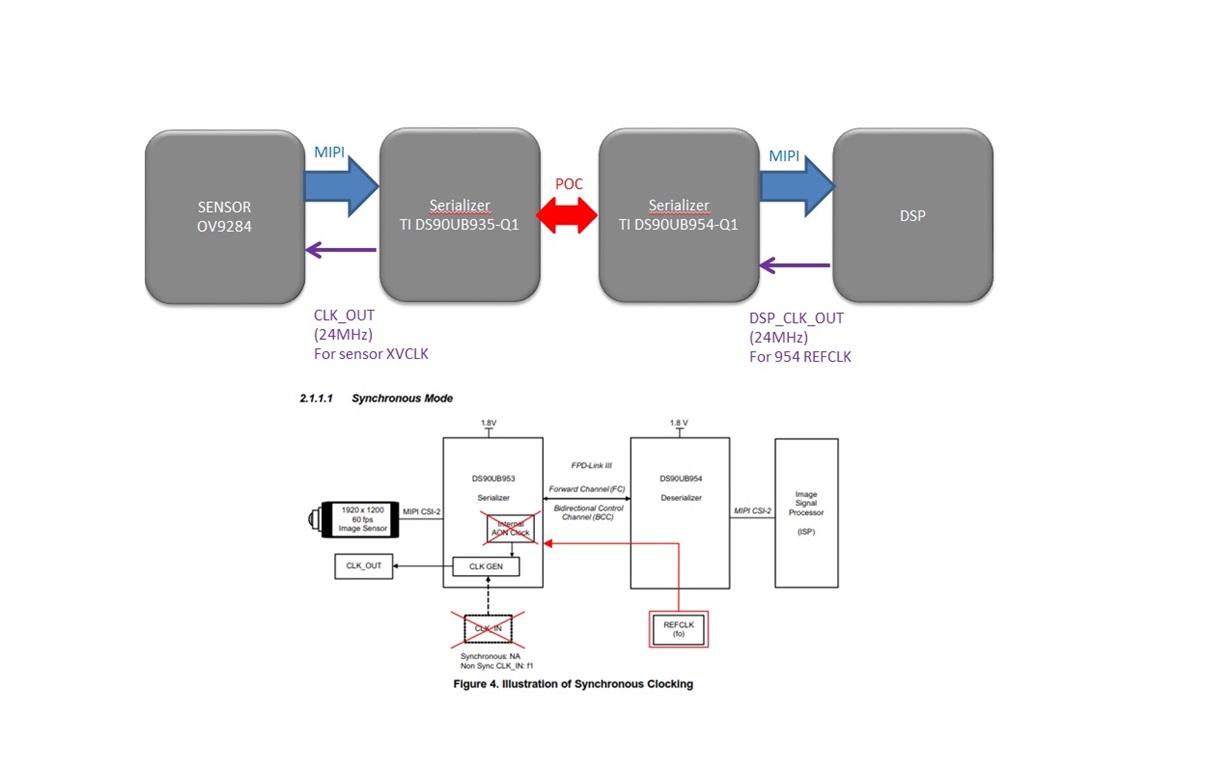

As following block diagram

DSP will provide REFCLK 24MHz for DS90UB954-Q1

At synchronous mode :

- How do we set Synchronous Mode register for 954 &953?

- At synchronous mode, how do we set 953 side CLK_OUT (24MHz) registers?

Best Regards