Other Parts Discussed in Thread: DSI-TUNER

The video on my display panel is flickering when I use these devices. How do I debug this issue?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Flickering images on a display panel can be caused by many factors. To help debug this issue, the first thing you should do is check that you’re configuring the device correctly using the DSI-Tuner (download here: https://tidrive.ext.ti.com/u/5B25JYQduSH2Hbkl/DSI%20Tuner%202.1.zip?l)

For single-channel DSI to single-channel LVDS, you can reference this video: https://training.ti.com/configuring-sn65dsi8x-single-channel-dsi-single-link-lvds-operation

For single-channel DSI to dual-channel LVDS, you can reference this FAQ as a guide: https://e2e.ti.com/support/interface/f/interface-forum/918890/faq-sn65dsi84-how-to-configure-the-sn65dsi84-and-sn65dsi85-for-single-channel-dsi-to-dual-channel-lvds

For dual-channel DSI to dual-channel LVDS, you can reference this video: https://training.ti.com/configuring-sn65dsi85-dual-channel-dsi-dual-link-lvds-operation

After correctly configuring the device with the collateral above, you should also check that the LVDS timing parameters (clock frequency, etc.) are within specification of your display panel. Additionally, verify that the video timing output from your DSI source matches what you are programming into the DSI83/DSI84/DSI85. This includes the DSI CLK frequency, active pixel data, and blanking pixel data. For example, if you put 300 MHz as the DSI CLK frequency in the DSI-Tuner, ensure that the frequency of the DSI CLK from the source is actually 300 MHz. Video input timing, register configuration, and the panel timing requirements all have to match up for the video streaming to work without errors.

You can also configure the device to output an internal test pattern using the DSI-Tuner. When configured for the test pattern, the device does not use the input DSI data. It only uses the DSI CLK or an external REFCLK to internally generate a test pattern based on the LVDS timing parameters. The test pattern looks like the below:

If the test pattern looks exactly like above, then any flickering seen when DSI data is used is likely due to an unstable DSI input or incorrect output from the DSI source. If there is flickering or incorrect color with the test pattern (e.g. the white strip appears gray) then the LVDS output has likely not been configured correctly for the display panel. Check that you’re using the correct format (Format 1 vs. Format 2) for the display panel, and that the LVDS timing is within spec.

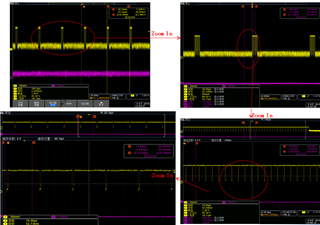

Another item to check is the burst/line time on the DSI input. Make sure the line time (time from HSYNC to HSYNC) on the DSI input matches the line time on the LVDS output. The line time on the LVDS output is the total amount of horizontal pixels divided by the LVDS clock frequency. You can measure the line time on the DSI input with an oscilloscope by zooming in on the data stream on of the data lanes like below:

You can also try using a clean external REFCLK as the clock source for the PLL instead of using the DSI CLK as the PLL source, as an excessively noisy DSI CLK may lead to an unstable LVDS clock output.