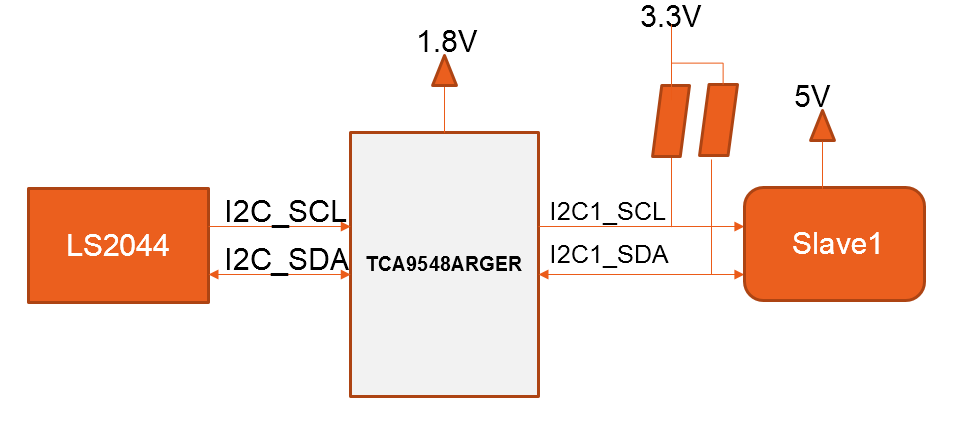

- Slave 1( Power supply module) is powered first from 5V and SDA,SCL shall powered with bias voltage of 3.3V ( derived from 5V internally) , but the power rail of VCC(1.8V) and IO voltage (3.3V)of TCA9548ARGER will be powered in after 48ms. Please find the below image for the circuit implementation

- Is this failure observed due to the power sequencing?

- Please provide the TI recommendation to mitigate this problem.

- Adding I2C buffer/isolator in SCL and SDA, if this solution works, please suggest part number for the same

- Adding Ferrite bead in series ( both SCL and SDA)