Tool/software: Linux

Hi all,

Our product use 954 to receive images from 913(720p) and 953(1080p). One or two bad images will be received in 954 side after switch from RIN1(720P) to RIN0(1080P).

When 954 switch from RIN0 to RIN1, there is no such issue.

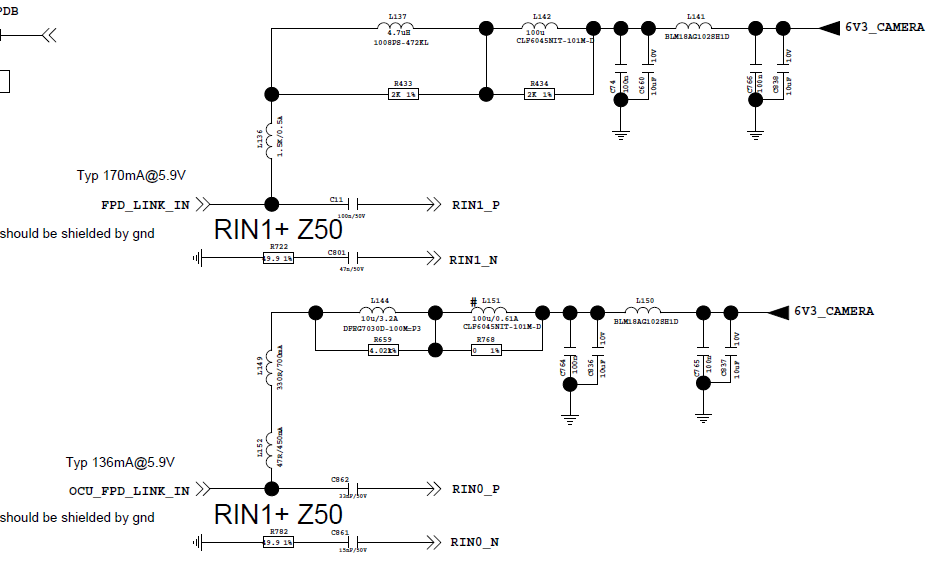

Architecture used as belows:

T T --------------RIN0-----------------913-------(720P@30fps yuv422)

| 954 |

|_ _| -----------------RIN1-----------------953-------(1080P@60fps yuv422)

The bad image looks like some pixel lines shifted or some pixel lines turns green. The bad images will be replaced by incoming right images quickly.

In 954 side could detect RX_PORT_STS1(0x4D) == 0x33, Bi-directional Control Channel CRC Error Detected, when this happens.

Any advices ? we need

thanks a lot