Hello,

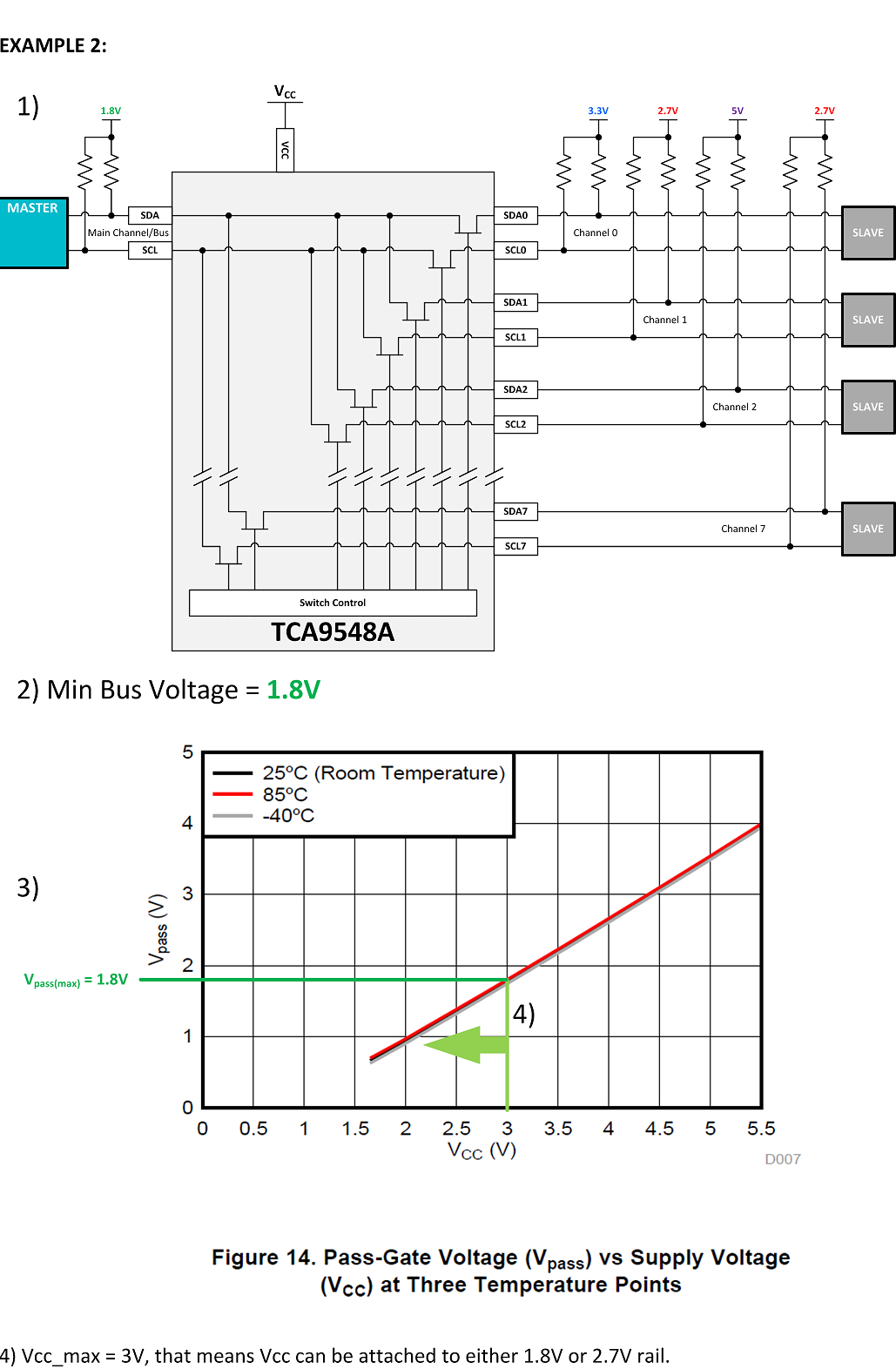

I have a question about the appropriate VCC on TCA9548A with a 1.8V master and 3.3V slaves. VCC is 2.5V. I used Example 2 in the post below to set this voltage.

It is my understanding 2.5V would be fine. However while reviewing the design, I found Vih to be 0.7 x Vcc (Table 6.3 of the data sheet) for A0-A2, SCL, SDA and /RESET.

Now, 0.7 x 2.5V is 1.75V which is too close to the master's 1.8V.

For one, I would like to know what I am missing in this analysis.

On the other hand, I would like to know if there is any performance penalty if I set VCC to 1.8V, as it would allow me to eliminate a level translator (1.8V > 2.5V) for the /RESET line.

Thanks in advance.