Other Parts Discussed in Thread: SN74AVC4T774

Hi,

Could you please provide some guidance on how resolve the following issue we are experiencing?

We have a TXS0108E IC to switch logic levels from 1.8V (Qualcomm Snapdragon 410) and 3.3V (STM32F100) and are having issues with many byte errors happening in the SPI communication.

The Qualcomm is the master and the STM is the slave. The SCLK is running at 1MHz (the TXS0108E's datasheet specifies that speeds up to 60Mbps should be doable for push-pull).

The TXS0108E is in the "vicinity" of the Qualcomm processor, and the STM32 is on the "far end".

We wrote some quick programs to send incrementing numbers out of the Qualcomm and be echoed back by the STM.

The result of this test is: approximately 60% of the bytes came back with errors. When we hooked up the oscilloscope the error rate became significantly larger, over 80% (the probes were set at 10X).

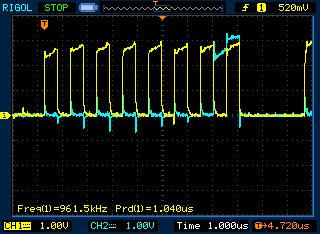

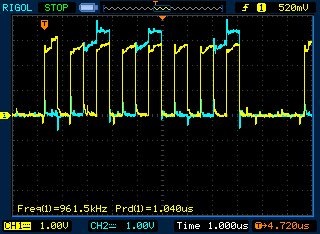

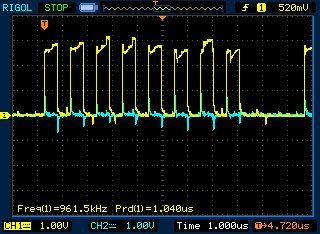

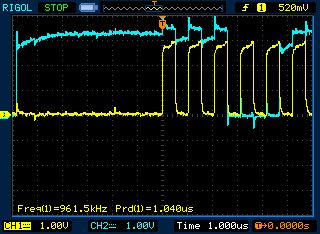

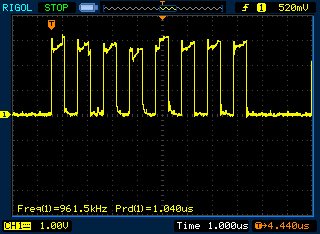

As you can see, transitions look fast but DC levels look bad. There is also some crosstalk and ringing.

Please refer to the following images:

Picture references:

SCLK is yellow

MOSI is blue

The oscilloscope probes were set at 10X

60% byte error rate without the oscilloscope

80% byte error rate with oscilloscope

This diagram shows the interconnection of the devices:

Motherboard

#####################################################

# SOM + Carrier Board "Zeus" board #

# ******************************************* ***************** #

# * (OPEN-Q 410 SOM) -> TXS0108E * ---------> * STM32F100 * #

# ******************************************* (20cm) ***************** #

# 1.8V 1.8V/3.3V 3.3V #

#####################################################

The probes were connected on the STM32 side.

The motherboard has SPI routed to 5 expansion slots. The board's SPI routing topology looks like this:

Empty Empty Empty

SOM | | |

Carrier board ---------------------------

| |

"Zeus" Empty

The linear trace length on the Moterboard in between the carrier board slot and the "zeus" board's slot is around 20cm. Thace width is around mostly 10 mils (8 mils when fanning out/into board to board connectors) and SCLK, MOSI and MISO rung alongside and are generally space 2x trace widths appart (where possible). The board to board connectors are 90 pin ones out of Hirose's DF40 series. The motherboard is a standard FR4, two layers, 1.6mm thick, 1Oz copper board.

Could you please advice?

Thank you!

Regards,

Alessandro