Hello,

I used LSF0204D for converting SPI Signal from 3v3-to-5V

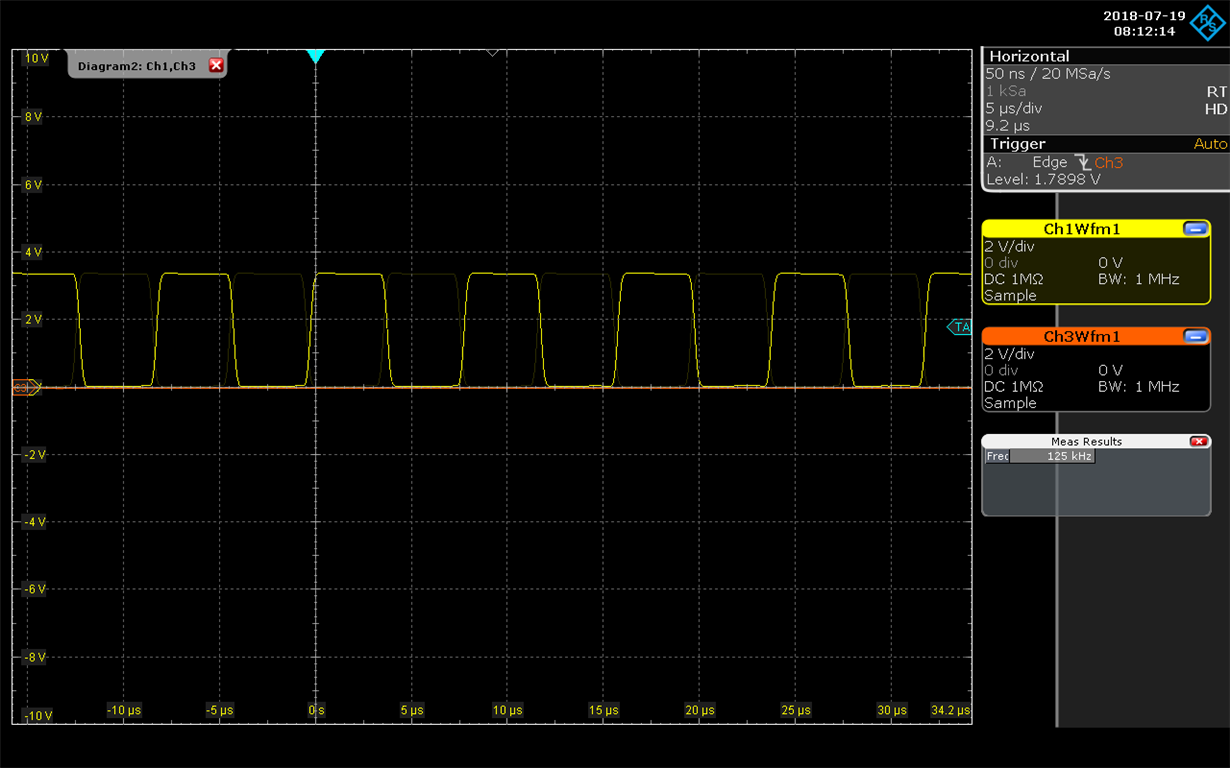

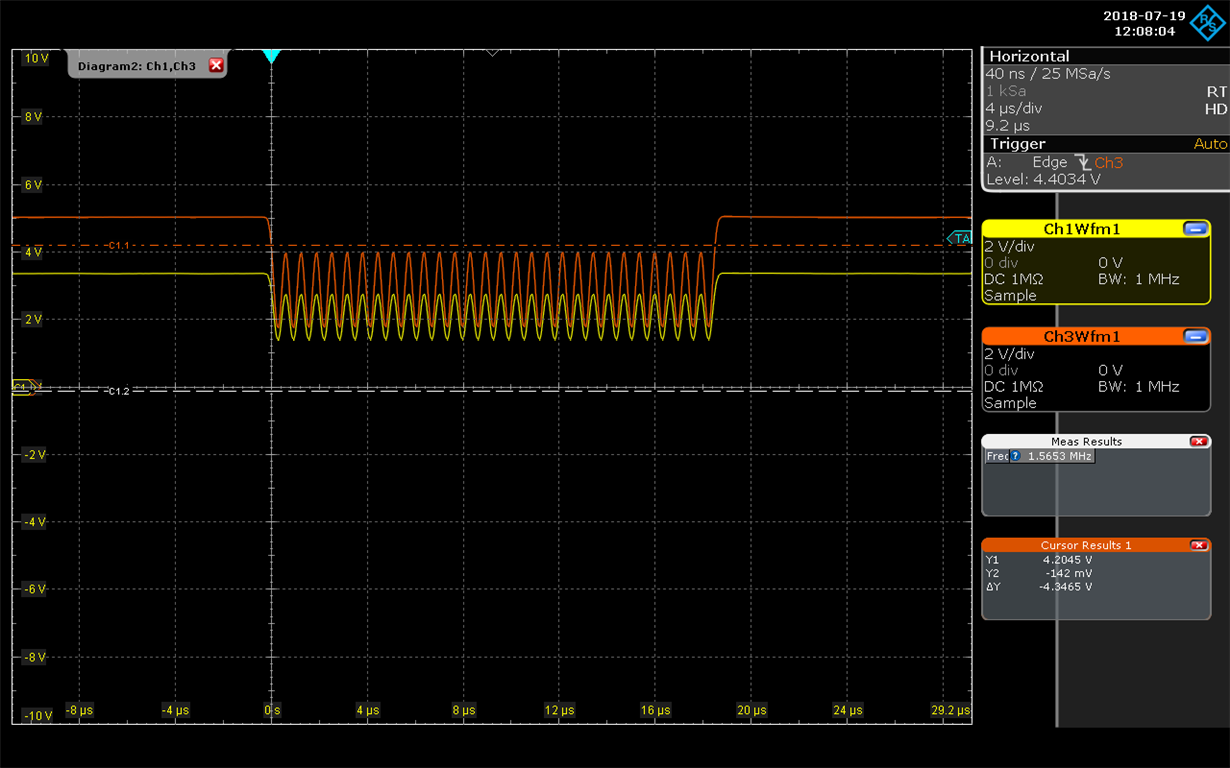

1) The MOSI signal which generated by µC give a clear and good quality at 3v3 level ( High = 3v3, Low = 0V). But if i connect the MISO-singal to LSF0204D, the Low-Level is shift to about 0v8 and therefore the output at 5V is also shift too (High = 5V, low = 1V) -> how can i have clear 0V at Low-Level at both sites?

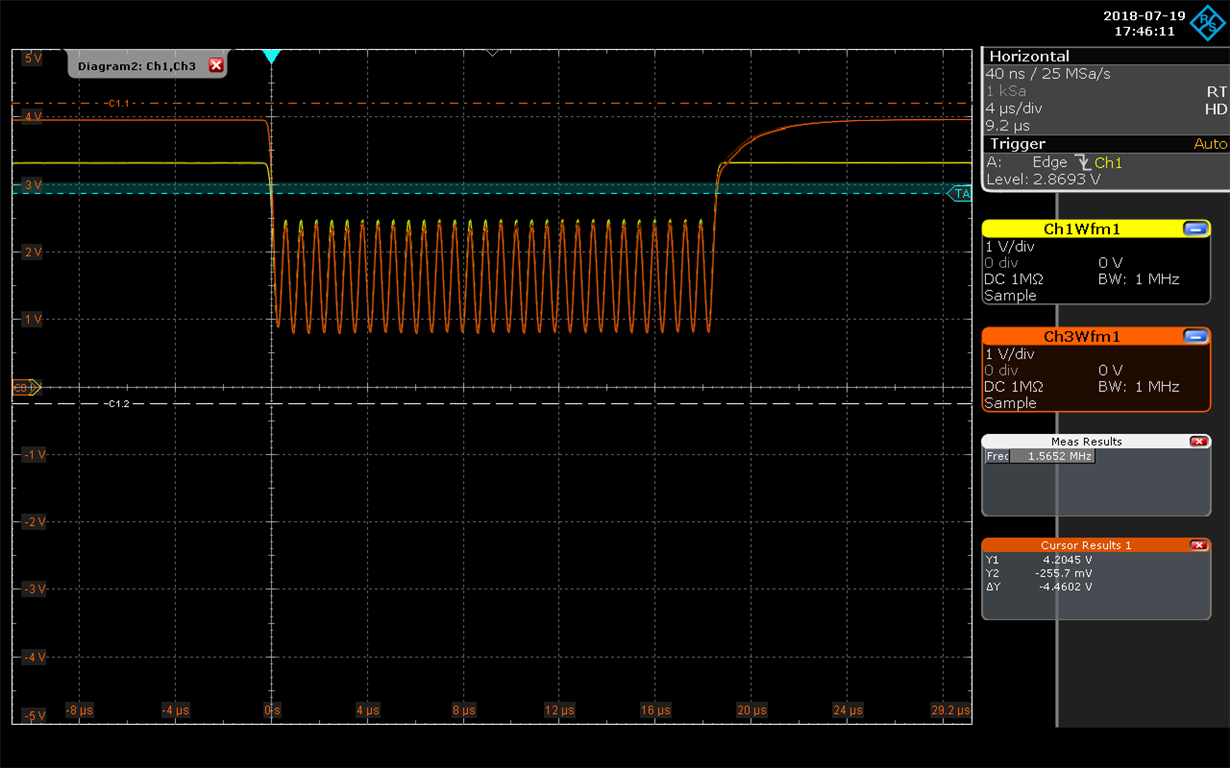

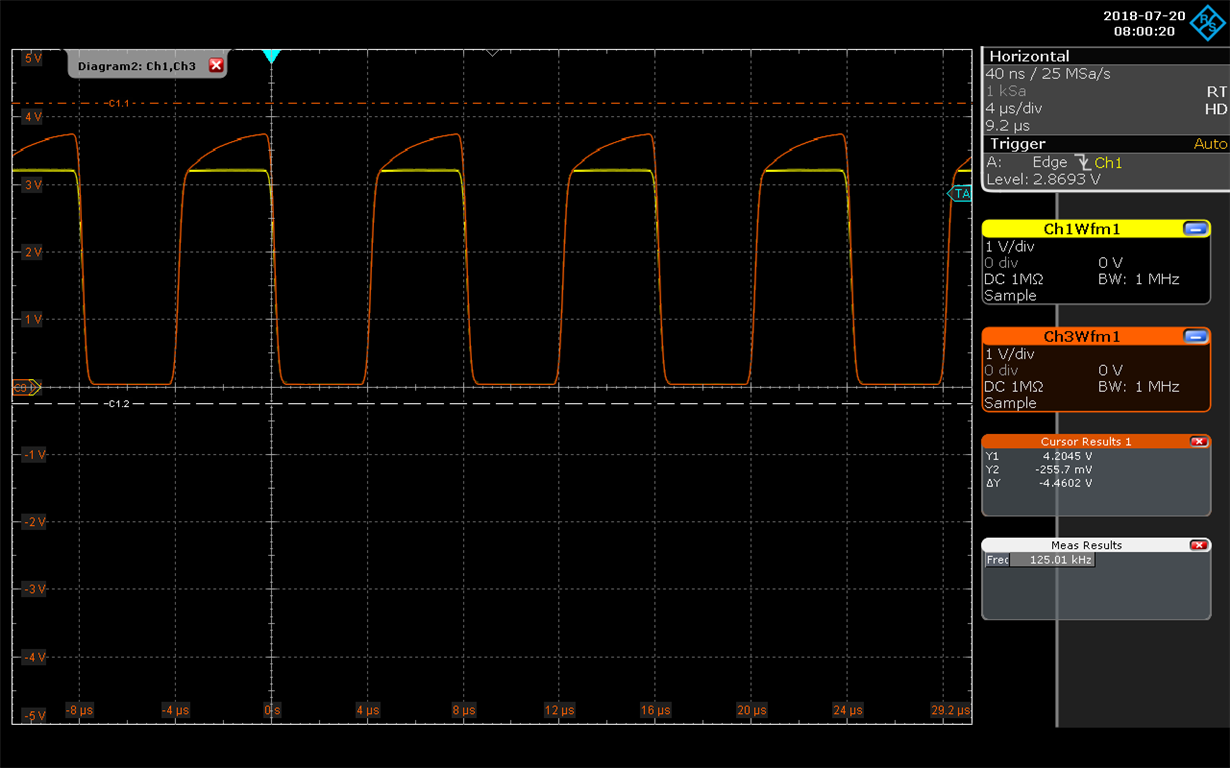

2) As I increased the SPI-speed, MOSI Speed at about 1,5Mhz, the signal of both sites has sinuous shape instead of square -> my question here is how should i define the resistor to have square signal at high-speed

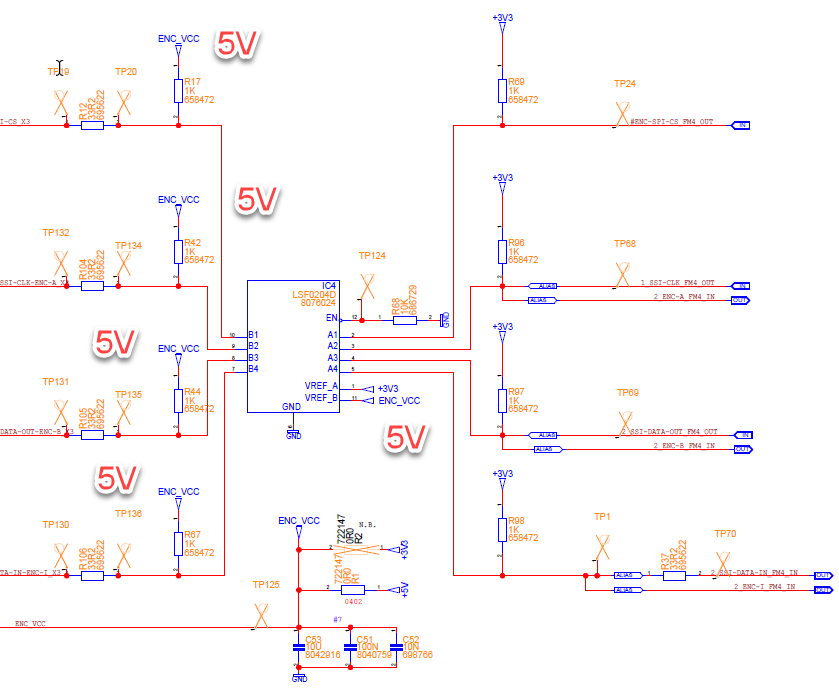

I attachted my schematic and also Oszi capture.

Thank your any advice.

Picture 1 with original SPI-MOSI without connecting with LSF0204D

Picture 2 of same singal MOSI when connecting with LSF0204D at both 3v3 and 5V site

Picture 3: System behavior at high frequency (1.5Mhz MOSI)

Picture 4: The circuit

Note that ENC_VCC is supplied at 5V. I also tried to change / removed serie resistor (33R2) and it did not changed the result.