Other Parts Discussed in Thread: ISOW7841

Hi,

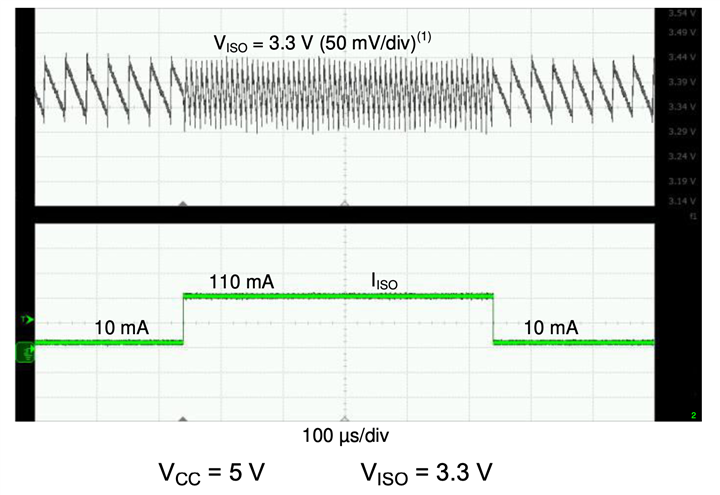

We are facing noise issues in the VDD pin, VISOOUT, and Vio pin. ( measured values are-> 124mv,200mv,101mv,),

Vio pin connected to 1.8v regulator that output noise 40mv only.

I'd like you to review my schematic. The schematic I will send the privet message.

Sincerely.