Hi,Expert

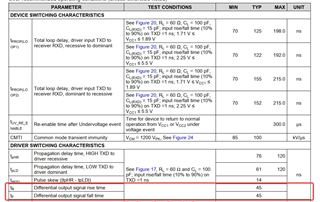

The tr/tf parameters in the ISO1042DWVR communication chip specification are as follows:

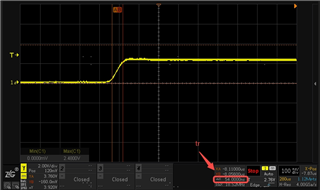

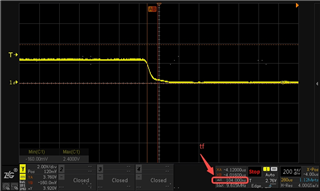

In the actual test, it is found that tf is 54ns and tf is 104ns, both of which exceed the typical values in the specification. Will it affect the communication quality?

In addition, there are only typical values in the specification, so what is the appropriate upper and lower limits without affecting the communication quality?