Other Parts Discussed in Thread: TIDA-00300

Hello, this topic is a continue of a previous one ISOW7841: ISOW7841 breaks down

The same customer has some additional questions:

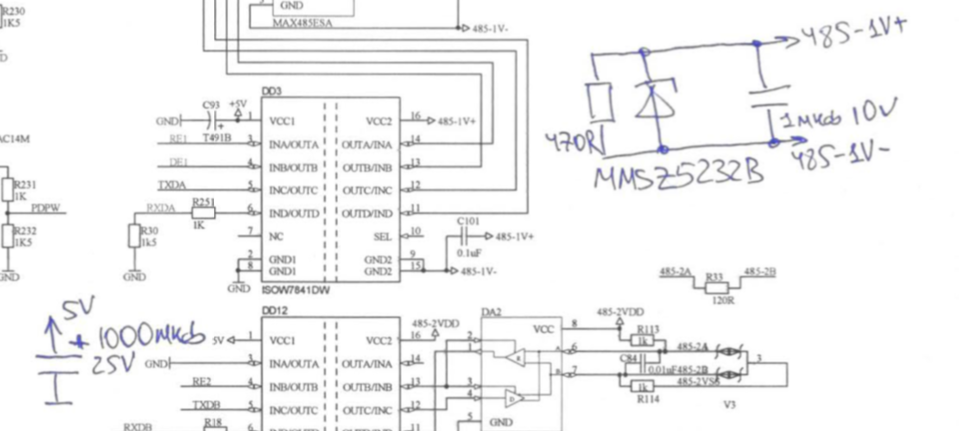

1. In TIDA-00300 design the output of ISOW7841 is protected by zener diode. But such solution is not described in data sheet. Is it mandatory to place a zener diode to protect ISOW7841?

2. In customer's application ISOW is used for different interfaces (485, CAN, RS-232).

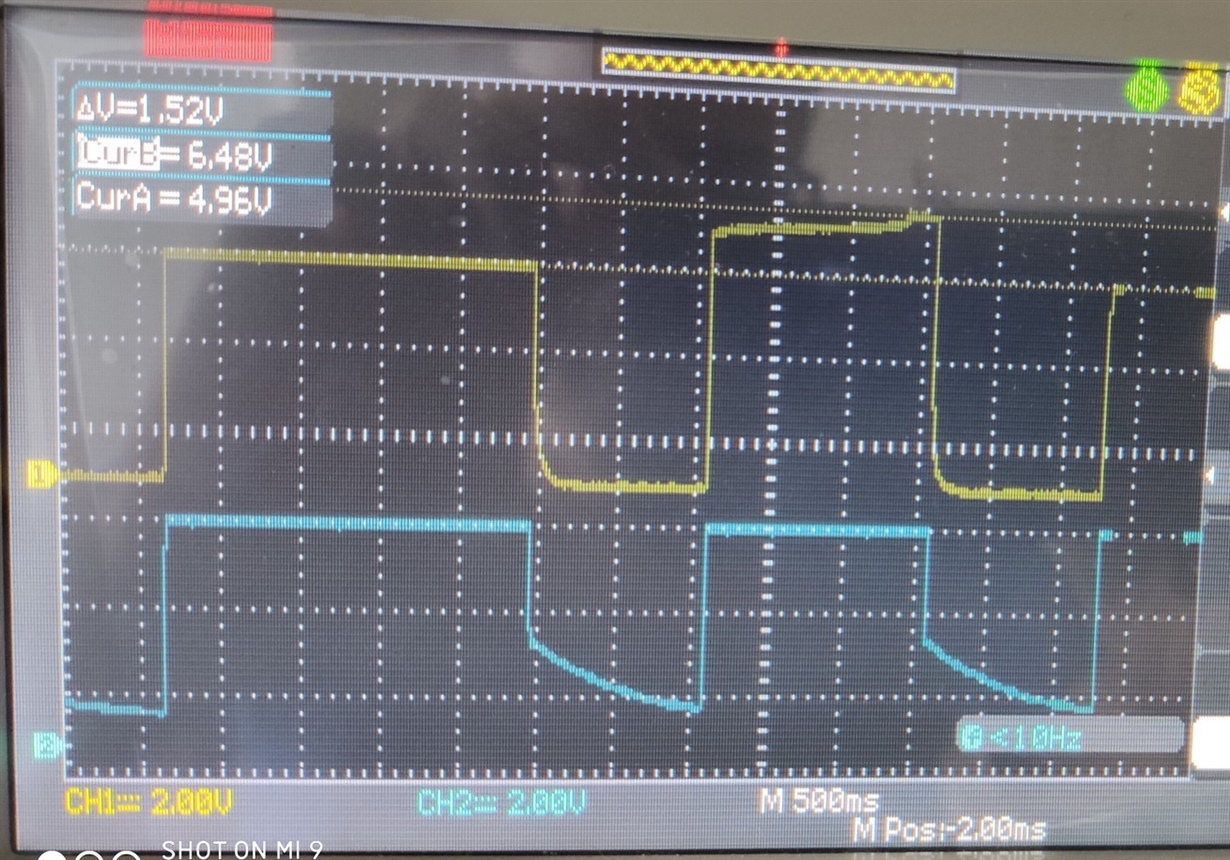

The current consumption from internal voltage converter of ISOW is not continuous, but changed in a pulsed way, because of used interfaces specialities.

Unlike TIDA-00300, customer's design does not contain an LED on ISOW output. This LED acts also as a passive load for internal power converter in ISOW.

Could be happen, that these two factors (pulsed current, lack of additional passive load) can lead to voltage increasing, when interface stops to consume the current?