Other Parts Discussed in Thread: LM5035,

Hi Team,

my customer has the following question. Could you please help us here.

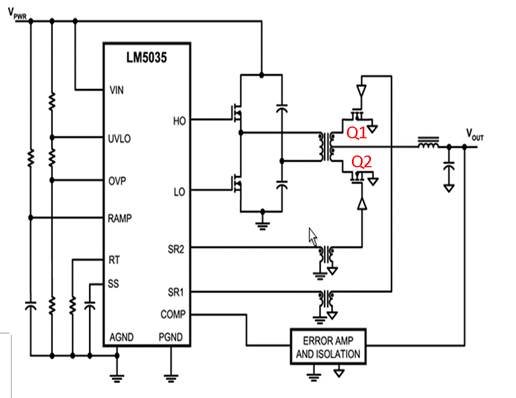

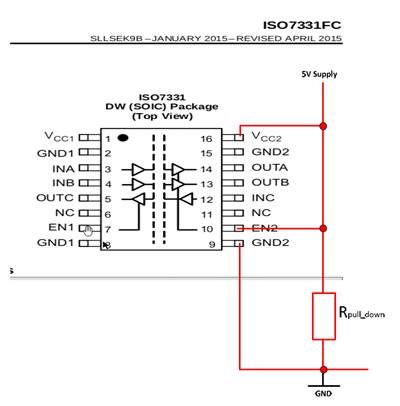

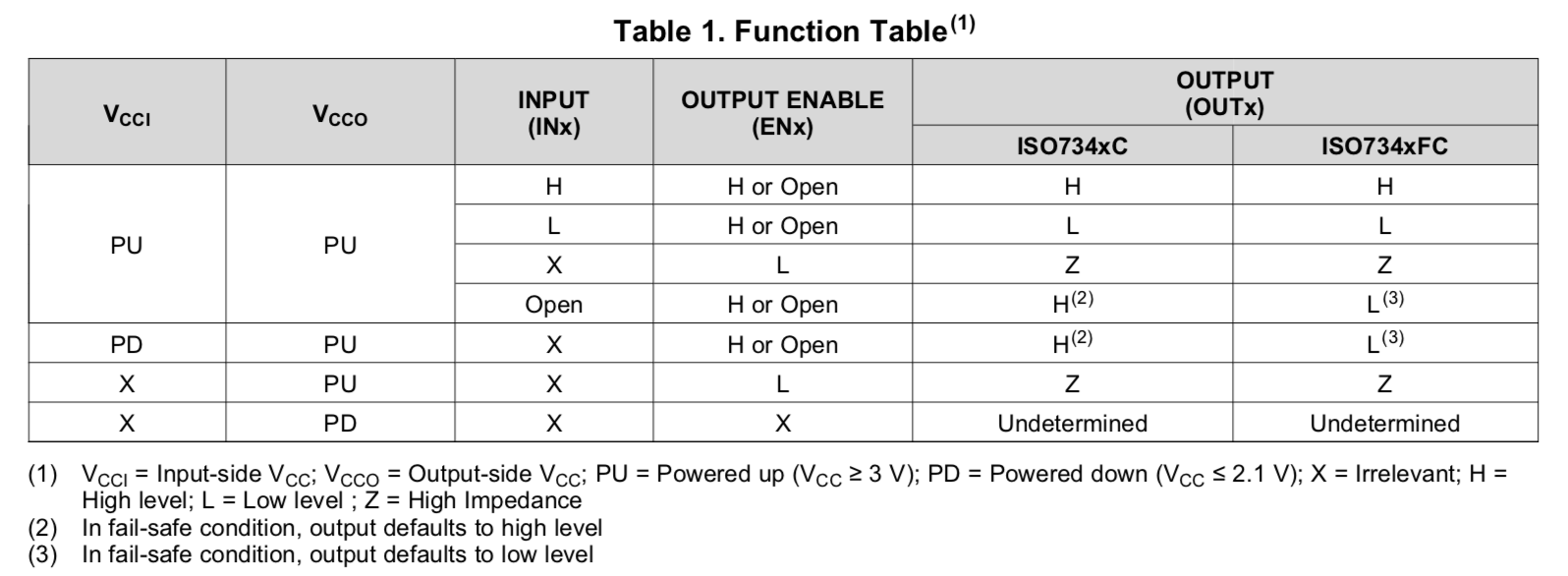

I have a technical question to a digital Isolator ISO7331F. Unfortunately the datasheet was not able to answer me this question. I use this Part for the synchronous Rectification Signals (SR1 and SR2) on the secondary side of a Power Supply Modul, which I realize with the TI Product LM5035.In my Application VCC1 is always Powered Up first and then VCC2. The SR1 and SR2 Signals will be transferred via INA and INB to OUT A and OUT B and then to a driver to switch on and off the MOSFETS Q1 and Q2. It is very important, that the Signals OUT A and OUT B must have a low Signal when VCC2 is not Powered at the beginning or fails. The may not have a HIGH Signal at the same time, otherwise I would have a short circuit. In the datasheet I just read UNDETERMINED. Does that mean, that they could have LOW OR HIGH or are the outputs TRI_STATE and I can Pull down OUT A and OUT B? Can I put them to a defined low Signal, by Pulling down the EN2, and after VCC2 is Powered EN2 has also a high Signal and the OUT A and OUT B are same as IN A and IN B. (See Figure 1 and 2 below)

Fig: 1

Fig 2:

The question is: Can I put OUT A and OUT B to a defined State (Low, in order to avoid short Circuit) when VCC2 is not available or is that not possible ?. Do you have an idea, if I can realize that with the ISO7331F or can you suggest another part?

Thank you in advance.

Best Regards,

Needhu