I want to measure the pulse wave width with LaunchPad 28379 Board .

In the begining, I use EPWM1A as input signal(to gpio26). I am sure my coding is correct.

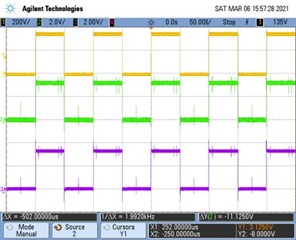

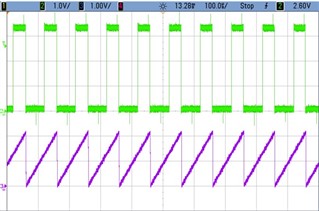

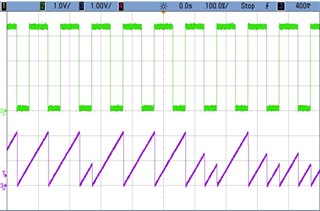

And the result as show below(Fig1 Fig2). The green wave is the input signal to gpio26. And purple wave is TSCTR in Ecap1. I use DAC to observe.

Also all the situation is correct.When detect the falling edge, the counter is reset. Otherwise, the counter is continue to counting until detect falling edge.

Fig1. Fig2.

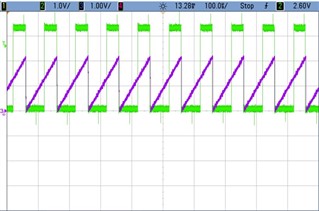

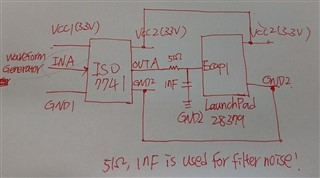

But because I want to measure wave which is isolated. So I use Ti IC iso7741. And circuit set up picture as below picture.

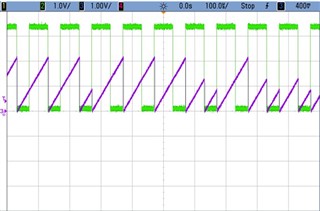

Also I use an oscilloscope to observe the waveform. Green waveform is input signal to gpio26(after 51+1nF signal).And purple waveform is TSCTR in Ecap1 which use DAC to observe.

And the result as show below. The rising edge and falling edge always detect error result.

Could you give me some suggestion:?

#include "F28x_Project.h"

#include <math.h>

Uint32 ECap1IntCount;

Uint32 ECap1PassCount;

Uint32 Ecap1ct1;

Uint32 Ecap1ct2;

Uint32 Ecap1ct4;

Uint32 Ecap1ct5;

Uint32 TSCTR1;

int j_Ecap1 =0;

float Ecap1duty;

int ready1=0;

int maincounter=0;

int mainarray=0;

float DVan;

float DVbn;

float DVcn;

float Vab;

float Vca;

float Vbc;

float Va;

float Vb;

float Vc;

//------------------------fundamental wave-----------------------

float theta=0;

float Comp1_EME=0;

float Comp2_EME=0;

float Comp3_EME=0;

#define frequency 60

#define Vd 0

#define Vq 3

#define REFERENCE_VREFHI 1

#define REFERENCE_VREF 1

#define DACA 1

#define DACB 2

#define DACC 3

#define REFERENCE REFERENCE_VREFHI

#define DAC_NUM DACA

volatile struct DAC_REGS* DAC_PTR[4] = {0x0,&DacaRegs,&DacbRegs,&DaccRegs};

//=====================DCA==============

//

// Function Prototypes

//

__interrupt void ecap1_isr(void);

__interrupt void thetaplus(void);

void InitECapture1(void);

void Fail(void);

void ConfigureGPIO(void);

void InitEPwm1Example(void);

void InitEPwm2Example(void);

void InitEPwm3Example(void);

void InitEPwm4Example(void);

void GPIOQua(void);

//

// Main

//

void main(void)

{

InitSysCtrl();

InitEPwm3Gpio();

InitECap1Gpio(26);

GPIO_SetupPinOptions(26, GPIO_INPUT, GPIO_SYNC);

GPIOQua();

ConfigureDAC(DAC_NUM);

ConfigureDAC(DACB);

ConfigureGPIO();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

PieVectTable.ECAP1_INT = &ecap1_isr;

PieVectTable.EPWM1_INT = &thetaplus;

EDIS;

InitECapture1();

ECap1IntCount = 0;

ECap1PassCount = 0;

IER |= M_INT3;

IER |= M_INT4;

//

// Enable eCAP INTn in the PIE: Group 3 __interrupt 1-6

//

PieCtrlRegs.PIEIER4.bit.INTx1 = 1;

PieCtrlRegs.PIEIER4.bit.INTx2 = 1;

PieCtrlRegs.PIEIER4.bit.INTx3 = 1;

PieCtrlRegs.PIEIER3.bit.INTx1 = 1;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;//?

CpuSysRegs.PCLKCR2.bit.EPWM1=1;

CpuSysRegs.PCLKCR2.bit.EPWM2=1;

CpuSysRegs.PCLKCR2.bit.EPWM3=1;

CpuSysRegs.PCLKCR2.bit.EPWM4=1;

CpuSysRegs.PCLKCR2.bit.EPWM5=1;

EDIS;

InitEPwm1Example();

InitEPwm2Example();

InitEPwm3Example();

InitEPwm4Example();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC =1;

EDIS;

EINT;

ERTM;

for(;;)

{

TSCTR1=ECap1Regs.TSCTR;

DAC_PTR[DAC_NUM]->DACVALS.all =(TSCTR1*0.15);

DAC_PTR[DACB]->DACVALS.all =(TSCTR1*0.15);

Comp1_EME = cos(theta) * Vd+ -sin(theta) * Vq;

Comp2_EME = cos(theta - 2.0943951023931953) * Vd + -sin(theta - 2.0943951023931953) * Vq;

Comp3_EME = cos(theta + 2.0943951023931953) * Vd + -sin(theta + 2.0943951023931953) * Vq;

EPwm2Regs.CMPA.bit.CMPA = (10.0 + Comp1_EME) * 0.05 * 5000.0;

EPwm2Regs.CMPB.bit.CMPB = (10.0 + Comp1_EME) * 0.05 * 5000.0+100.0;

EPwm3Regs.CMPA.bit.CMPA = (10.0 + Comp2_EME) * 0.05 * 5000.0;

EPwm3Regs.CMPB.bit.CMPB = (10.0 + Comp2_EME) * 0.05 * 5000.0+100.0;

EPwm4Regs.CMPA.bit.CMPA = (10.0 + Comp3_EME) * 0.05 * 5000.0;

EPwm4Regs.CMPB.bit.CMPB = (10.0 + Comp3_EME) * 0.05 * 5000.0+100.0;

//GpioDataRegs.GPACLEAR.bit.GPIO18 = 1;

}

}

void InitECapture1()

{

ECap1Regs.ECEINT.all = 0x0000; // Disable all capture __interrupts

ECap1Regs.ECCLR.all = 0xFFFF; // Clear all CAP __interrupt flags

ECap1Regs.ECCTL1.bit.CAPLDEN = 0; // Disable CAP1-CAP4 register loads

ECap1Regs.ECCTL2.bit.TSCTRSTOP = 0; // Make sure the counter is stopped

//

// Configure peripheral registers

//

ECap1Regs.ECCTL2.bit.CONT_ONESHT = 1; // One-shot

ECap1Regs.ECCTL2.bit.STOP_WRAP = 1; // Stop at 2 events

ECap1Regs.ECCTL2.bit.SWSYNC = 1; //同步所有的Ecap時鐘

ECap1Regs.ECCTL1.bit.CAP1POL = 0; // Risingedge

ECap1Regs.ECCTL1.bit.CAP2POL = 1; // Falling edge

ECap1Regs.ECCTL1.bit.CTRRST1 = 0; //Abs

ECap1Regs.ECCTL1.bit.CTRRST2 = 1; // Difference operation

ECap1Regs.ECCTL2.bit.SYNCI_EN = 1; // Enable sync in

ECap1Regs.ECCTL2.bit.SYNCO_SEL = 0; // Pass through

ECap1Regs.ECCTL1.bit.CAPLDEN = 1; // Enable capture units

ECap1Regs.ECCTL2.bit.TSCTRSTOP = 1; // Start Counter

ECap1Regs.ECCTL2.bit.REARM = 1; // arm one-shot

ECap1Regs.ECCTL1.bit.CAPLDEN = 1; // Enable CAP1-CAP4 register loads

ECap1Regs.ECEINT.bit.CEVT2 = 1; // 2 events = __interrupt

}

__interrupt void ecap1_isr(void)

{

GpioDataRegs.GPASET.bit.GPIO18 = 1;

ECap1PassCount++;

ready1=1;

Ecap1ct4=ECap1Regs.CAP1;

Ecap1ct5=ECap1Regs.CAP2;

GpioDataRegs.GPACLEAR.bit.GPIO18 = 1;

ECap1Regs.ECCLR.bit.CEVT2 = 1;

ECap1Regs.ECCLR.bit.INT = 1;

ECap1Regs.ECCTL2.bit.REARM = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP4;

}

__interrupt void thetaplus(void)

{

GpioDataRegs.GPDTOGGLE.bit.GPIO111 = 1; // GPIO34 = 1

theta=theta+0.03758;

if(theta>=6.28)

{

theta=0;

}

EPwm1Regs.ETCLR.bit.INT = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP3;

}

void ConfigureDAC(Uint16 dac_num)

{

EALLOW;

DAC_PTR[dac_num]->DACCTL.bit.DACREFSEL = REFERENCE;

DAC_PTR[dac_num]->DACOUTEN.bit.DACOUTEN = 1;

DAC_PTR[dac_num]->DACCTL.bit.LOADMODE=0;

DAC_PTR[dac_num]->DACVALS.all = 0;

DELAY_US(10); // Delay for buffered DAC to power up

EDIS;

}

void ConfigureGPIO(void)

{

EALLOW;

GpioCtrlRegs.GPAPUD.bit.GPIO18 = 0; // Enable pullup on GPIO34

GpioCtrlRegs.GPAMUX2.bit.GPIO18 = 0; // GPIO34 = GPIO34

GpioCtrlRegs.GPADIR.bit.GPIO18 = 1; // GPIO34 = output

GpioDataRegs.GPACLEAR.bit.GPIO18 = 1; // GPIO34 = 1

GpioCtrlRegs.GPAPUD.bit.GPIO19 = 0; // Enable pullup on GPIO34

GpioCtrlRegs.GPAMUX2.bit.GPIO19 = 0; // GPIO34 = GPIO34

GpioCtrlRegs.GPADIR.bit.GPIO19 = 1; // GPIO34 = output

GpioDataRegs.GPACLEAR.bit.GPIO19 = 1; // GPIO34 = 1

GpioCtrlRegs.GPBPUD.bit.GPIO32 = 0; // Enable pullup on GPIO34

GpioCtrlRegs.GPBMUX1.bit.GPIO32 = 0; // GPIO34 = GPIO34

GpioCtrlRegs.GPBDIR.bit.GPIO32 = 1; // GPIO34 = output

GpioDataRegs.GPBCLEAR.bit.GPIO32 = 1; // GPIO34 = 1

GpioCtrlRegs.GPCPUD.bit.GPIO67 = 0; // Enable pullup on GPIO34

GpioCtrlRegs.GPCMUX1.bit.GPIO67 = 0; // GPIO34 = GPIO34

GpioCtrlRegs.GPCDIR.bit.GPIO67 = 1; // GPIO34 = output

GpioDataRegs.GPCCLEAR.bit.GPIO67 = 1; // GPIO34 = 1

GpioCtrlRegs.GPDPUD.bit.GPIO111 = 0; // Enable pullup on GPIO34

GpioCtrlRegs.GPDMUX1.bit.GPIO111 = 0; // GPIO34 = GPIO34

GpioCtrlRegs.GPDDIR.bit.GPIO111 = 1; // GPIO34 = output

GpioDataRegs.GPDCLEAR.bit.GPIO111 = 1; // GPIO34 = 1

GpioCtrlRegs.GPAPUD.bit.GPIO2 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPACLEAR.bit.GPIO2 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO2 = 1; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO2 = 1; // GPIO6 = output

GpioCtrlRegs.GPAPUD.bit.GPIO3 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPACLEAR.bit.GPIO3 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO3 = 1 ; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO3 = 1; // GPIO6 = output

GpioCtrlRegs.GPAPUD.bit.GPIO4 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPACLEAR.bit.GPIO4 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO4 = 1; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO4 = 1; // GPIO6 = output

GpioCtrlRegs.GPAPUD.bit.GPIO5 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPASET.bit.GPIO5 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO5 = 1; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO5 = 1; // GPIO6 = output

GpioCtrlRegs.GPAPUD.bit.GPIO6 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPACLEAR.bit.GPIO6 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO6 = 1; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO6 = 1; // GPIO6 = output

GpioCtrlRegs.GPAPUD.bit.GPIO7 = 0; // Enable pullup on GPIO6

GpioDataRegs.GPASET.bit.GPIO7 = 1;

GpioCtrlRegs.GPAMUX1.bit.GPIO7 = 1; // GPIO6 = GPIO6

GpioCtrlRegs.GPADIR.bit.GPIO7 = 1; // GPIO6 = output

EDIS;

}

void GPIOQua()

{

//5x2xTSYSCLKOUT

GpioCtrlRegs.GPACTRL.bit.QUALPRD3 = 2;//Qualification sampling period for GPIO24 to GPIO31,2:QUALPRDx = PLLSYSCLK/4

GpioCtrlRegs.GPAQSEL2.bit.GPIO24 = 1,0;//1,0 Qualification (6 samples)

GpioCtrlRegs.GPAQSEL2.bit.GPIO25 = 1,0;//1,0 Qualification (6 samples)

GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 1,0;//1,0 Qualification (6 samples)

}

void InitEPwm1Example()

{

EALLOW;

// Setup TBCLK

EPwm1Regs.TBPRD = 5000; // Set timer period 5000 TBCLKs (10kHz)

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

// Set Compare values

// EPwm1Regs.CMPA.bit.CMPA = 1000; // Set compare A value

// EPwm1Regs.CMPB.bit.CMPB = 1000+50; // Set Compare B value

// Setup counter mode

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up and down

EPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

// Setup shadowing

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set actions

//EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

//EPwm1Regs.AQCTLA.bit.CAD = AQ_SET;

//EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

//EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

// Interrupt where we will change the Compare Values

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero event

EPwm1Regs.ETSEL.bit.INTEN = 1; // Enable INT/// Original 1

EPwm1Regs.ETPS.bit.INTPRD = ET_1ST; // Generate INT on 3rd event

EDIS;

}

void InitEPwm2Example()

{

EALLOW;

// Setup TBCLK

EPwm2Regs.TBPRD = 5000; // Set timer period 5000 TBCLKs (10kHz)

EPwm2Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm2Regs.TBCTR = 0x0000; // Clear counter

// Set Compare values

// EPwm2Regs.CMPA.bit.CMPA = 1000; // Set compare A value

// EPwm2Regs.CMPB.bit.CMPB = 1000+50; // Set Compare B value

// Setup counter mode

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up and down

EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

// Setup shadowing

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set actions

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm2Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm2Regs.AQCTLB.bit.CBD = AQ_CLEAR;

// Interrupt where we will change the Compare Values

EPwm2Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero event

EPwm2Regs.ETSEL.bit.INTEN = 1; // Enable INT/// Original 1

EPwm2Regs.ETPS.bit.INTPRD = ET_3RD; // Generate INT on 3rd event

EDIS;

}

void InitEPwm3Example()

{

EALLOW;

// Setup TBCLK

EPwm3Regs.TBPRD = 5000; // Set timer period 2000 TBCLKs

EPwm3Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm3Regs.TBCTR = 0x0000; // Clear counter

// Set Compare values

//EPwm3Regs.CMPA.bit.CMPA = 2500; // Set compare A value

//EPwm3Regs.CMPB.bit.CMPB = 2500+50; // Set Compare B value

// Setup counter mode

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up and down

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1;

// Setup shadowing

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set actions

EPwm3Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm3Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm3Regs.AQCTLB.bit.CBD = AQ_CLEAR;

// Interrupt where we will change the Compare Values

EPwm3Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero event

EPwm3Regs.ETSEL.bit.INTEN = 1; // Enable INT/// Original 1

EPwm3Regs.ETPS.bit.INTPRD = ET_3RD; // Generate INT on 3rd event

EDIS;

}

void InitEPwm4Example()

{

EALLOW;

// Setup TBCLK

EPwm4Regs.TBPRD = 5000; // Set timer period 2000 TBCLKs

EPwm4Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm4Regs.TBCTR = 0x0000; // Clear counter

// Set Compare values

//EPwm4Regs.CMPA.bit.CMPA = 4000; // Set compare A value

//EPwm4Regs.CMPB.bit.CMPB = 4000+50; // Set Compare B value

// Setup counter mode

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up and down

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Disable phase loading

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1;

// Setup shadowing

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on Zero

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

// Set actions

EPwm4Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm4Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm4Regs.AQCTLB.bit.CBD = AQ_CLEAR;

// Interrupt where we will change the Compare Values

EPwm4Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; // Select INT on Zero event

EPwm4Regs.ETSEL.bit.INTEN = 1; // Enable INT/// Original 1

EPwm4Regs.ETPS.bit.INTPRD = ET_3RD; // Generate INT on 3rd event

EDIS;

}