Other Parts Discussed in Thread: ISO7820LL

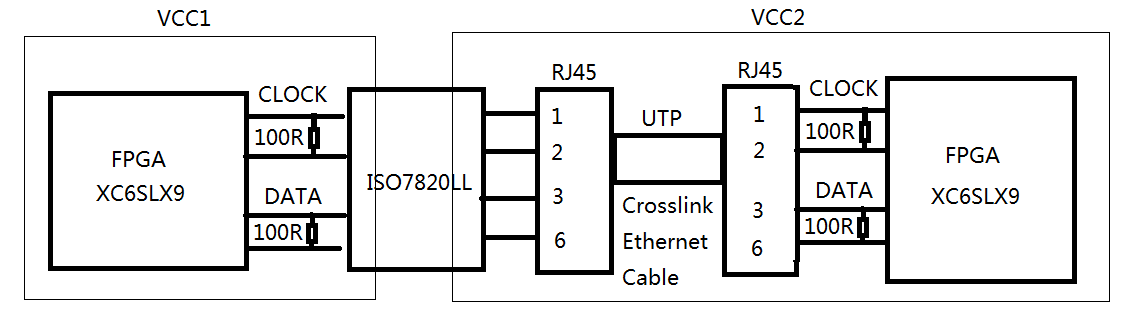

Through RJ45 and two groups of unshielded twisted pair, we transmit LVDS‘s clock and data。

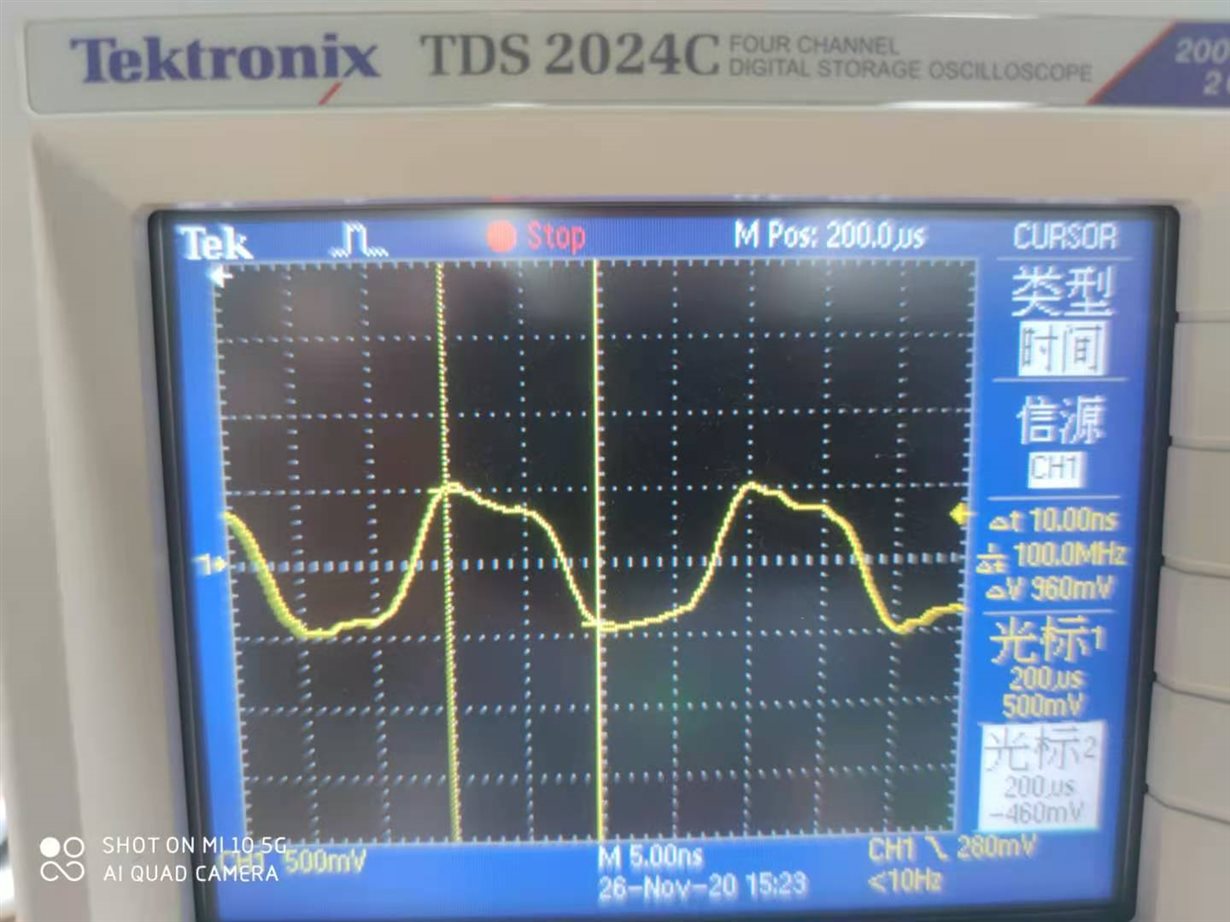

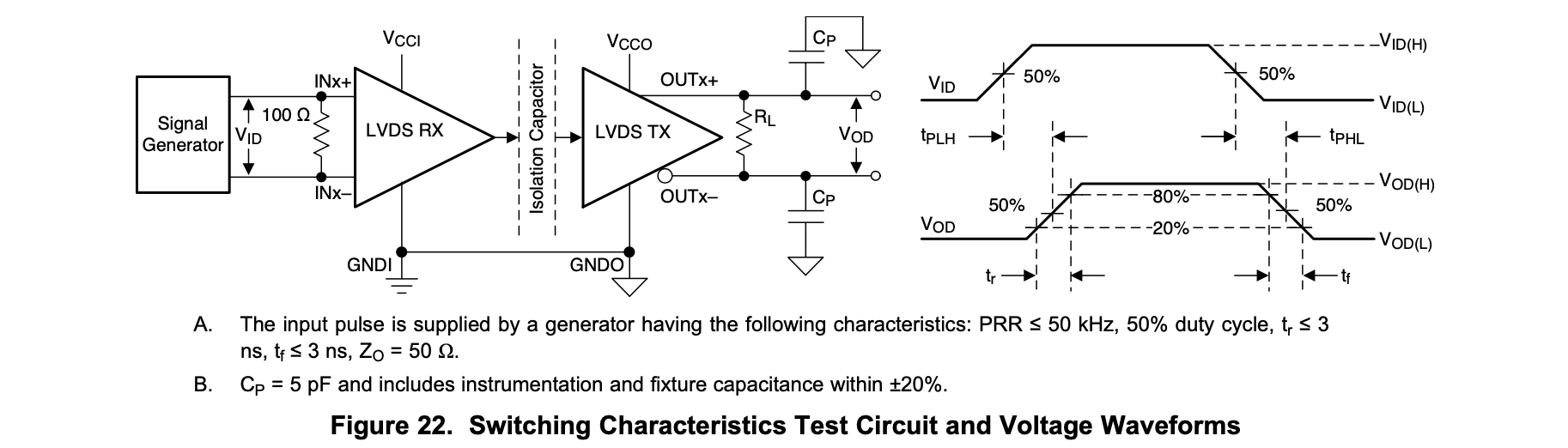

when use ISO7720LL one time as isolation ship。The frequency of 20Mbps is good,but the frequency of 25Mbps is bad,the bit error rate is very high。

Is this problem caused by the impedance discontinuity of the cable and PCB ?

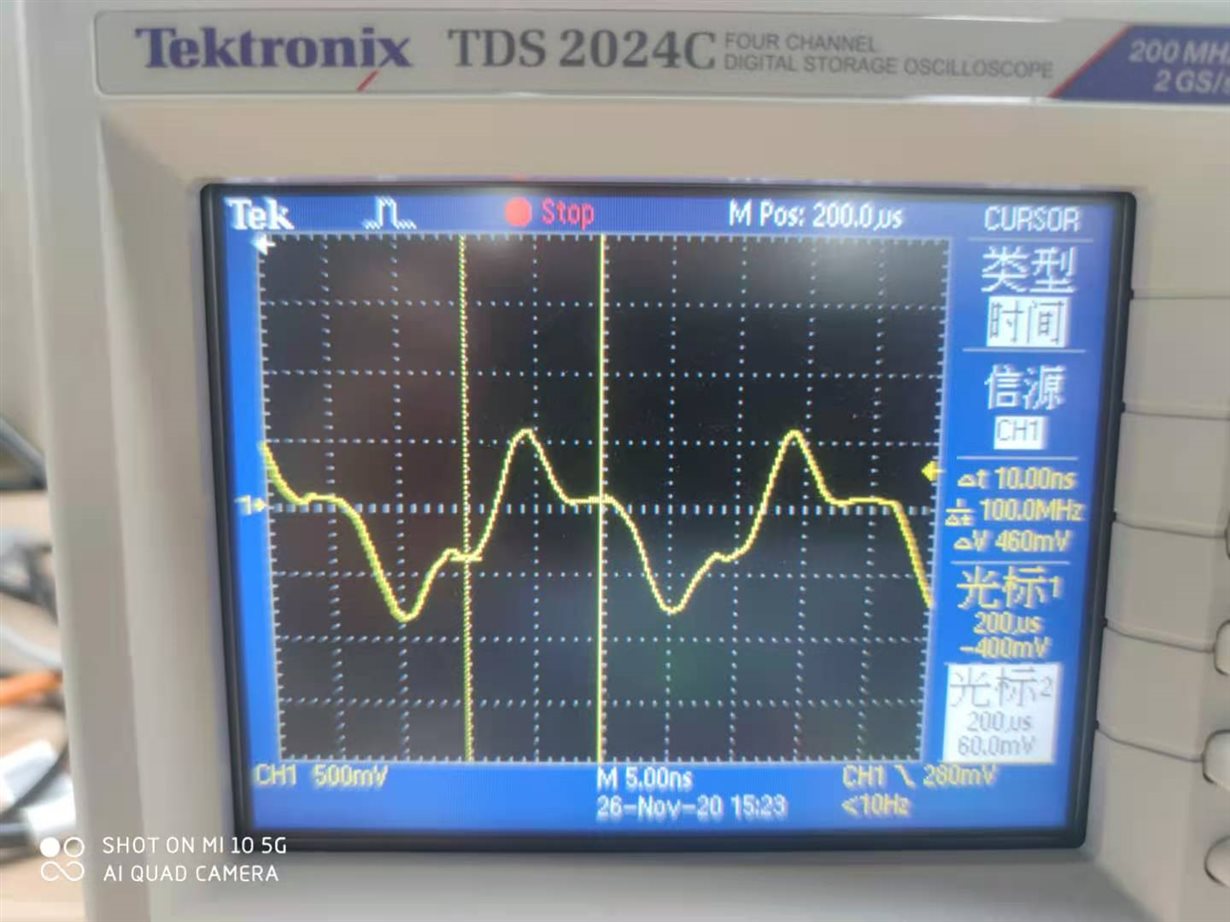

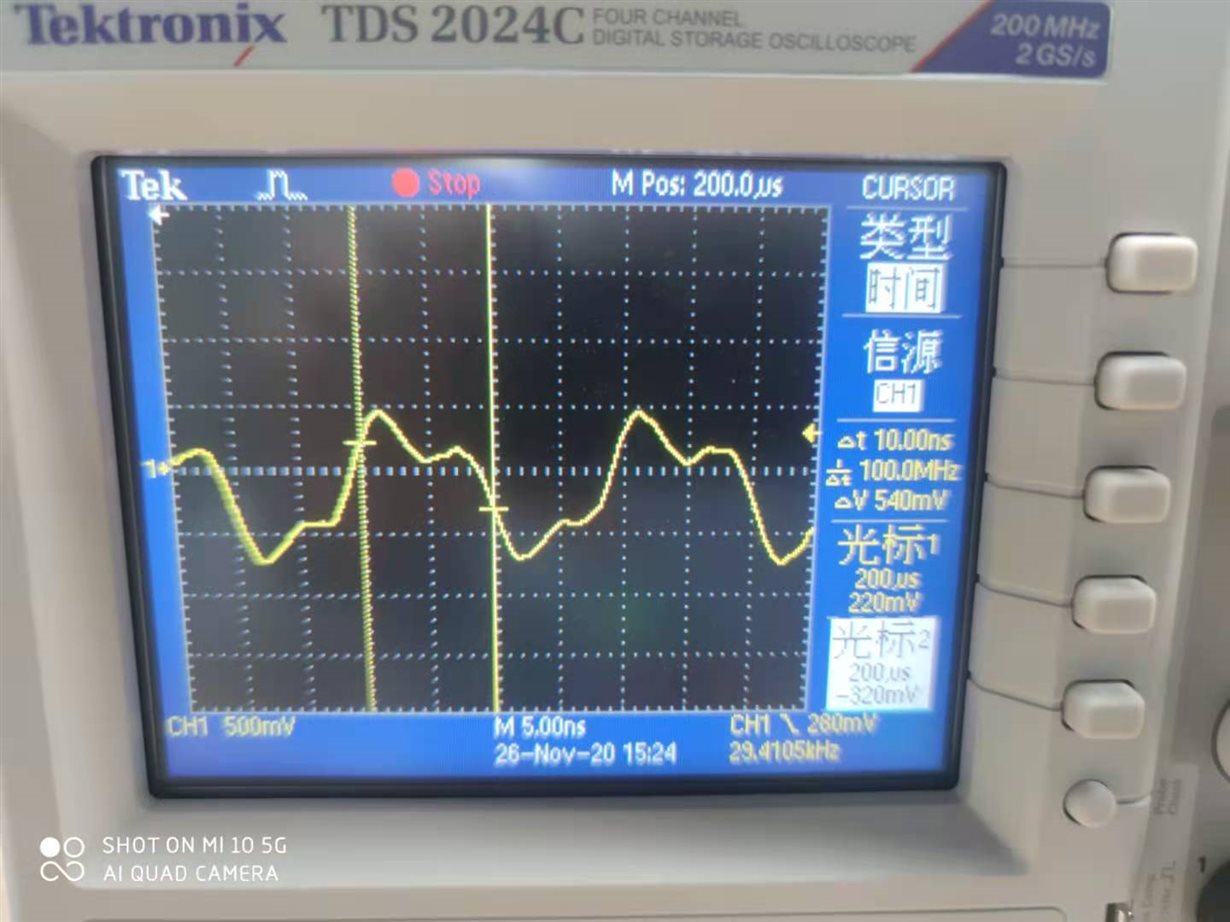

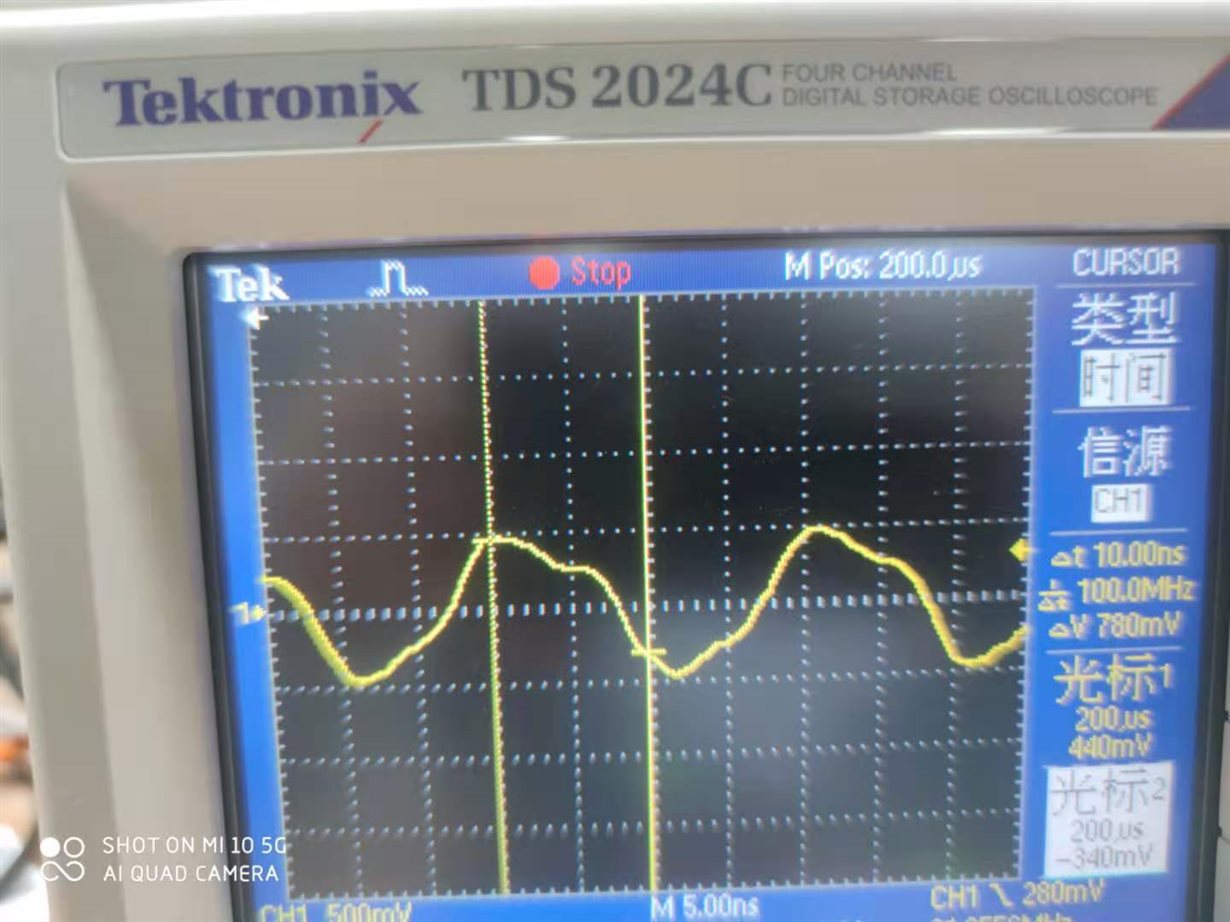

As shown in the figure below, when use ISO7720LL two times as isolation ship。No matter how low the frequency is, the bit error rate is very high?

Is this method of two times isolation correct?