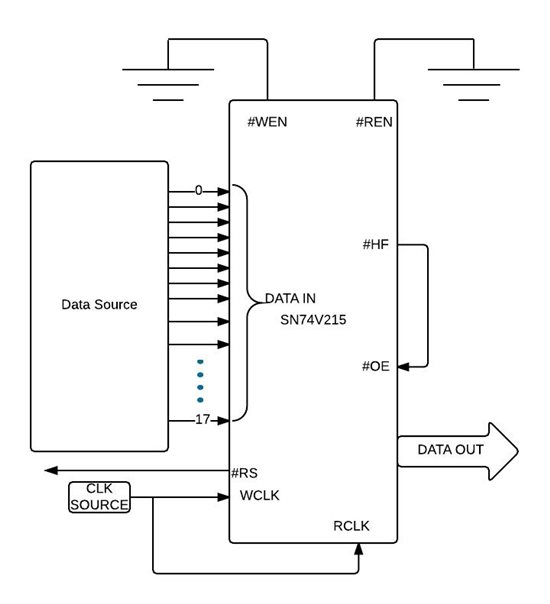

In the FIFO SN74V215, the 18 input data lines are connected to a data source and the clock supply is connected to WCLK and #WEN(active low) is by default tied to ground, so that it is ready at the first instance itself to take the input inside the FIFO.

Consider the case that the setup is initially OFF. At an instance, both the data source and the FIFO are turned ON, but the data source has not produced any output for some clock ticks (just the source and FIFO are connected and turned ON and the CLOCK is running without any data).

What will be recorded inside the FIFO if this is the case? Will there be some junk inside? I don't want any data to be written inside the FIFO until the data source has produced the Data. What should I do?