Other Parts Discussed in Thread: LSF0204, SN74AXC4T774, SN74AXC2T245

Hi,

We are using LSF0204QPWRQ1 in the design. We have few doubts with respect to design.

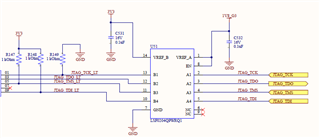

1)Schematic1:

The LSF0204 is used to translate JTAG lines from 3V3 to 1V8 and vice versa.

1)As per JTAG recommendation, we already provided 1kohm for JTAG TMS and TDI. Whether this pull-up will have any impact on the operation of the level translator? The direction is from 1V8 to 3V3.

2)Whether we need to provide pull up for JTAG TDO on the 1V8 side (the leakage is more than 1uA and TDO direction is from 3V3 to 1V8)?

3)For TCK, as per recommendation pull down is used. But we believe , TCK will always be low. TCK flows from 1V8 to 3V3. When TCK from 1V8 side outputs high, the pass transistor will turn off. Hence TCK on the 3V3 side will be pulled low. When TCK from 1V8 outputs low, the pass transistor will turn on and the TCK on the 3V3 side will be low. Is this analysis correct?What can be done for this application so that TCK can be transmitted flawlessly?

4)Whether receivers need pull-up resistors if driven by Push-pull?

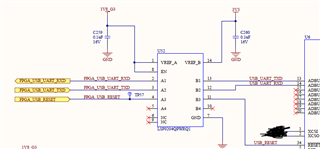

2)Schematics 2:

1)Whether FPGA_USB_UART_RXD needs pull-up resistor? It is driven from 3V3 to 1V8

2)Whether UART_USB_RXD needs pull-up resistor? It is driven from 1V8 to 3V3

3)Pull-down resistor of 10kohm value is provided at FPGA_USB_RESET net(on 3V3 side). RESET is driven from 1V8 to 3V3. Whether the analysis below is correct?

When 1V8 side is in high impedance state(push-pull), the FPGA_USB_RESET is pulled down and this will turn on the pass MOSFET and the low voltage will be available at 3V3 side. When 1V8 side outputs high, the voltage at 1V8 side will be high causing the MOSFET to turn off. 3V3 side will be floating and RESET signal will be in unknown state. So whether pull-up is needed at the USB_RESET net?If pull-up is properly sized, can we drive 3V3 side low when 1V8 is low and 3V3 side high when 1V8 side is high(note: pull-down will be present in 1V8 side)?

4)What is the threshold input voltage to Ax/Bx at which the pass MOSFET will turn off?

Please provide your answers

Thanks

Viswa