Hi Team,

Could you pls see below question description. There are detailed waveform screenshot attached. Thanks

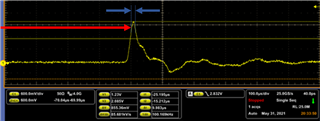

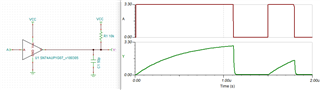

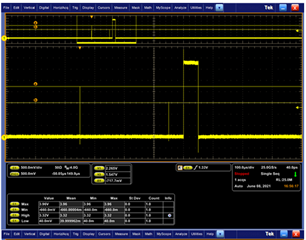

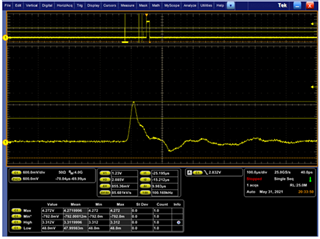

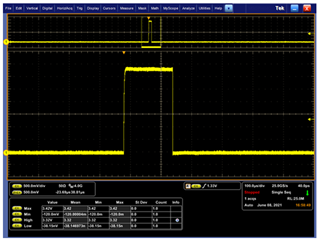

- Customer found there is crosstalk glitch at the IC input, but there are no spike at the output side. They want to know what the conditions the crosstalk glitch may cause the IC output falsely. You can see the some spikes reach the Vih(2V) here.

Best,

Stanley