Other Parts Discussed in Thread: SN74LVC1G17, SN74LVC1G99, SN74LVC1G14, SN74HCS125

Hi team,

Regarding SN74LVC1G126DBVR and SN74LVC1G125DBVR, can you help me answer the following questions? Thanks!

1, Regarding the turn-on level threshold of OE of SN74LVC1G126DBVR:

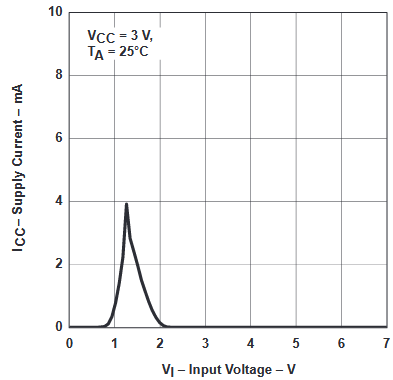

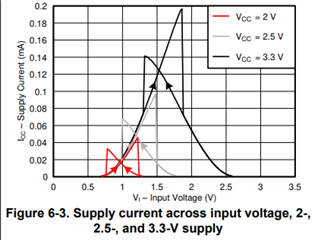

As shown in the figure above, the power supply is 3V, and the A input of SN74LVC1G126DBVR is directly grounded. When the input level of OE rises from 0, it should be at least 2V to turn on and output 0, but the actual measurement is about 1.36V and the output is 0. I don't know what is the reason?

2, About SN74LVC1G125DBVR/OE turn-on level threshold_01:

As shown in the figure above, when the /OE of SN74LVC1G125DBVR starts to rise from 0, does the output turn off when it rises to 0.8V (output high impedance), or does it need to rise to 2V before the output turns off (output high impedance)?

3. About the intermediate state of SN74LVC1G125(6)DBVR:

When input A is standard 0 or 3V and OE is between 0.8V and 2V, what will be the output? How much will the power consumption increase at this time? Will it damage the IC?

When OE is turned on and input A is between 0.8V and 2V, what will be the output? How much will the power consumption increase at this time? Will it damage the chip?

What will the output be when both OE and input A are between 0.8V ~ 2V? How much will the power consumption increase at this time? Will it damage the chip?

Thanks a lot!

Thanks & best regards,

Wendy