Hi there!

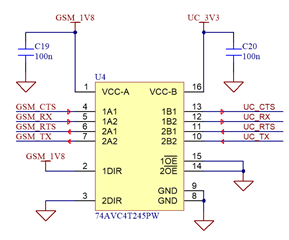

I want to use the level translator between a microcontroller (+3V3 I/O level) and a cellular (GSM) module (+1V8 I/O level). The cellular module generates a +1V8 I/O reference from it's +4V2 supply. Here is the circuit:

When the cellular module's +4V2 power supply is switched off by the microcontroller, I do not want to source parasitic current to the module via the TX and RTS pins. The datasheet states that it supports partial power-down.

I want to tie 1/OE and 2/OE directly to GND but the datasheet states: "To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver."

Is there a potential problem with this approach? Please explain.

Thanks in advance,

Pieter