Other Parts Discussed in Thread: SN74AUC2G126, SN74AUC1G126

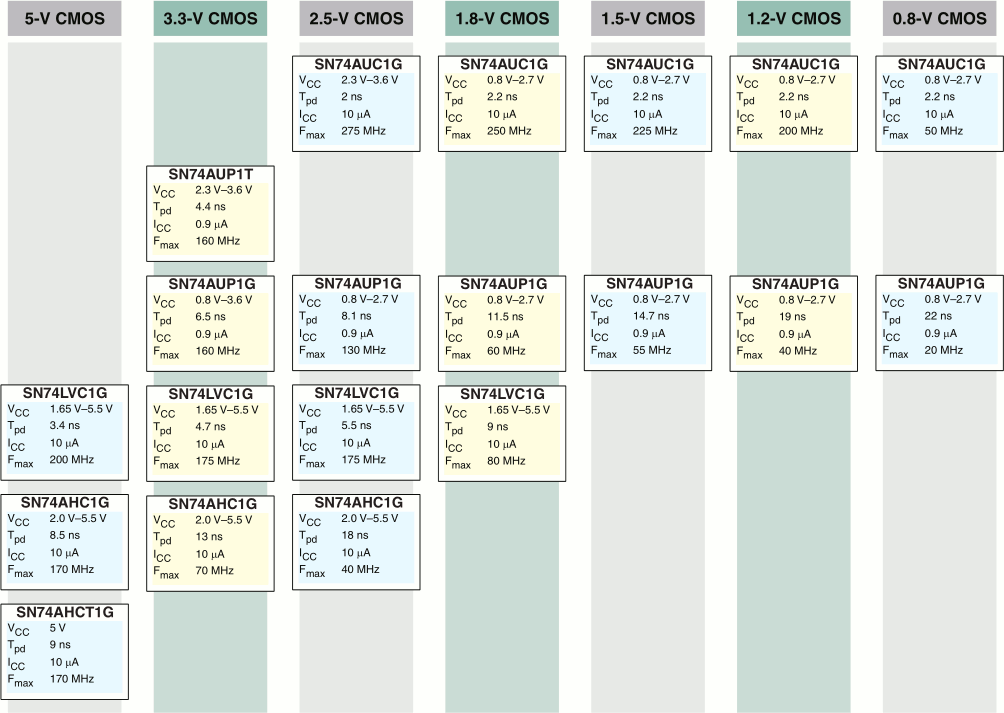

With VDD = 1.8V± 5%, can this device support 66.66MHz input square wave?

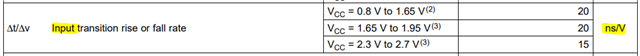

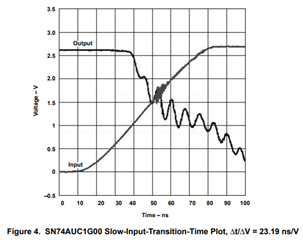

What is the expected Tr/Tf for CL = 15pF in this case?

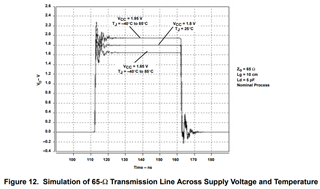

Has this device been observed to be used in applications that buffer a clock signal?

(I worry about jitter and clock signal degradation...)