Hi Experts,.

SN74HC573A-Q1 is used in customer for BMS. The project is under DV. There is fault output of SN74HC573A-Q1, it will cause the whole system down.

This device need be fixed before 9/10. So it can catch the PV test progress.

Here is the description for this issue:

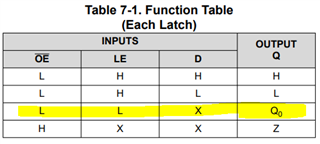

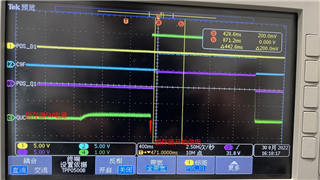

When the power up, the LE and /OE are pulled down, the input(D) is low, but sometimes the output is high. we find that before the power up, the power pin is 0.8V, it's cause by the MCU. Our competitor who have a same device doesn't have this issue. Could you help to explain this issue? thanks.

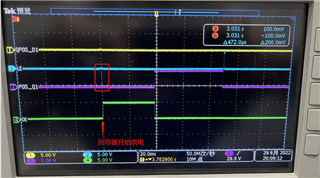

The datasheet of SN74HC573A-Q1 is described that the /OE need keep high before the power up, but in this system, it can't meet this requirement. Because if they pull up the /OE, the PCB need redesign and our device can't catch the PV timeline. I also let customer to do the test in current board(Fly a line between 5V and /OE and SN74HC573A-Q1 is powered by 5V), it also has a power sequence for /OE and 5V, it can cause the fault output. When the software power down the OE, the output is still high. It also need pull up LE and pull down D1, in that time, Q1 is pull down with D1. But the initial will fault before software pull up LE. Could you also help to explain this? Why the Q1 is high output when /OE is pull down? thanks.

Best Regards

Songzhen Guo