Other Parts Discussed in Thread: SN74AUP1G08

Tool/software:

Hi,

I am working with several TI logic devices that state they support Ioff protection and Partial power down protection. I have searched and read through just about everything I can find online both from TI and other vendors to try and better understand the dynamics of the Ioff protection mechanism.

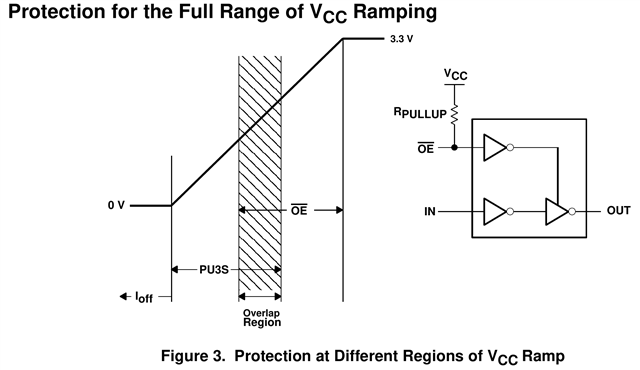

In particular what happens when an IC like the D-FLOP referenced here has an input pin connected to a low impedance voltage source that can deliver considerable current. Such as a Li-ion cell, and then the Vcc pin is relatively slowly raised from 0 to its working voltage. The specifications for Ioff feature are not entirely clear about the lower threshold on Vcc when Ioff activates. Furthermore there is no information about what happens in the transition region when Ioff is deactivating and the device has not reached its minimum Vcc, still further Even if Vcc has exceeded min Vcc on voltage it may still be at a lower voltage than an I/O pin and we might still see the ESD diodes forward biased. In these conditions we could in fact theoretically see quite a large voltage difference between Vcc and an I/O pin and potentially damaging current.

Is this actually true or are there multiple protection taking place that continue to isolate the I/O pins until Vcc exceed the I/O voltages? I see nothing in the datasheet of the DFLOP to suggest this but I have read a application note from TI that discuss PU3S protection. I do not believe the D-FLOP has this mechanism, but interestingly this app note has a somewhat confusing paragraph regarding Ioff. I quote.

"For devices with only an IOFF specification or without any of the IOFF, PU3S, and precharge specifications (for example, LVC and ALVC), GND and VCC need to be powered up to the recommended operating level before output or I/O ports can be exposed to any live signal. A device output or I/O port can be exposed to a live signal with VCC = 0 V if IOFF is specified for that port. But an input port, with IOFF, can handle a live signal when VCC = 0 V and while VCC is ramping up or ramping down. This is why an input port connection can occur any time after the GND connection in the power-up sequence, if that port has IOFF specified."

This suggests that the behaviour of input pins is different to that of output pins, but is this true and does this only apply to the device families mentioned?

I am using other devices that also state they have Ioff protection but again in these cases also, the threshold voltages for protection and the behaviour of the devices in the transition as Vcc ramps up or down and the differences in input versus output pins is not entirely clear.

Could you please help me with a more detailed description of the internal structure of these circuits on which pins it applies and how to read the datasheets to extract any relevant data, then I can decide under which circumstances I need to consider external current limiting. I have read several app notes from TI even ones specifically referencing what information is contained on datasheets in respect to Ioff function, but even these do not clearly answer my questions.

I look forward to some clarity,

All the best.