Hi,

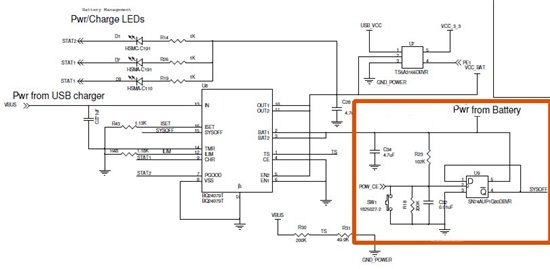

I have a simple circuit (given to me via some TI source) that allows a momentary ON Switch to toggle a D flip-flop so that the output can be used to turn on and off the battery power to the remainder of the circuit board. So, this simple circuit is always powered to allow the power switch to work, so it is very important that it consume as little power as possible.

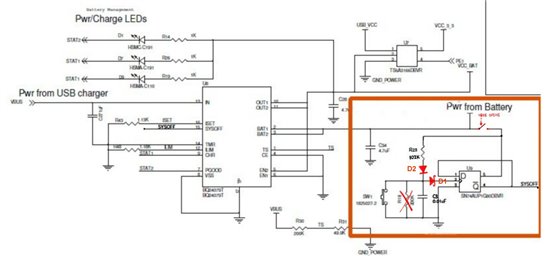

I planned on using the circuit 'as is' with the ultra low power SN74AUP1G80. Then I noticed the original circuit is switching 3.3V whereas I was switching a 3.7V LiIon battery. Unfortunately, the battery can charge to 4.1V which is more than the CLK input can withstand! Soooo, I put a divider, R18 = 200k, to limit the voltage on as a bandaid fix. This was only a temporary fix as the circuit is now drawing even more current.

The solution was to get a higher power flip-flop, SN74LVC1G80, and remove R18. This solution, overall, uses less current.

It really seemed like the simplest solution. The problem is Q* stays high and does not toggle when the momentary ON switch is pulsed low on CLK!

I even tried doubling the cap value across the CLK from 0.01uF to 0.02uF, even though it does not appear to be switch bounce.

Please note, in closing, that I am without a scope, so I am hoping one of you guys will look at this and figure it out just by inspection, or give me an easy test to try that does not involve a scope.

Thanks in advance!

Kevin Kreger