Dear All,

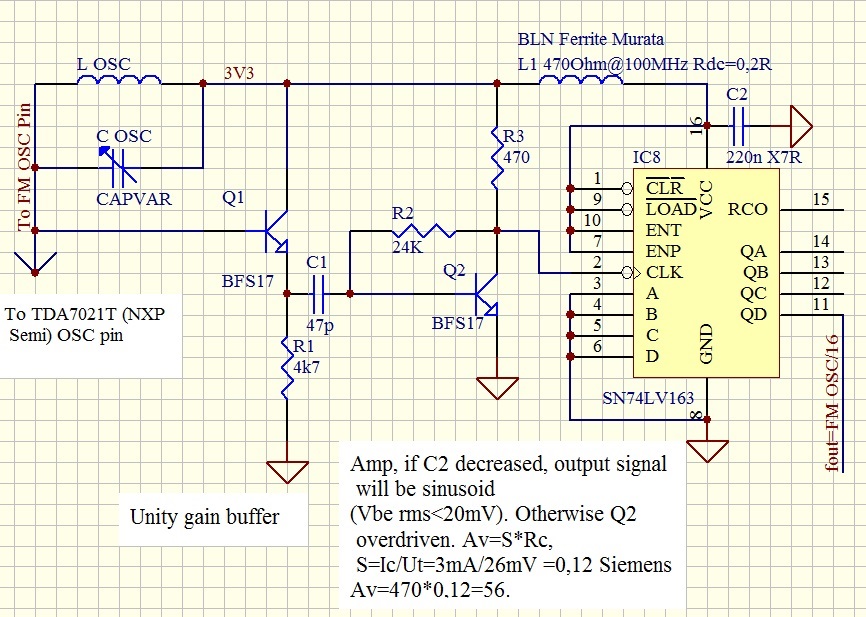

I would like to use a 74LV163AD 4-bit counter as precaler (1/16) applied to FM radio receiver oscillator (fosc=100MHz). Supply volatge is 3V3.

The oscillator level is ca 240mV RMS. Prior to the '163 there would be a two-stage RF amp to increase level to

ca 1-2Vp-p using BFS17 transistors (first in common collector secod in common emitter operation). Unfortunately OSC level cannot be so high to avoid radiation. The '163 CLK

input would directly connected to the out of RF amplifier which is biased to VCC/2.

I would like to ask wheter you have any experiments about similar applications when "standard" logic family is used instead of dedicated

prescaler circuits?

Many thanks for the comments in advance!