Hi

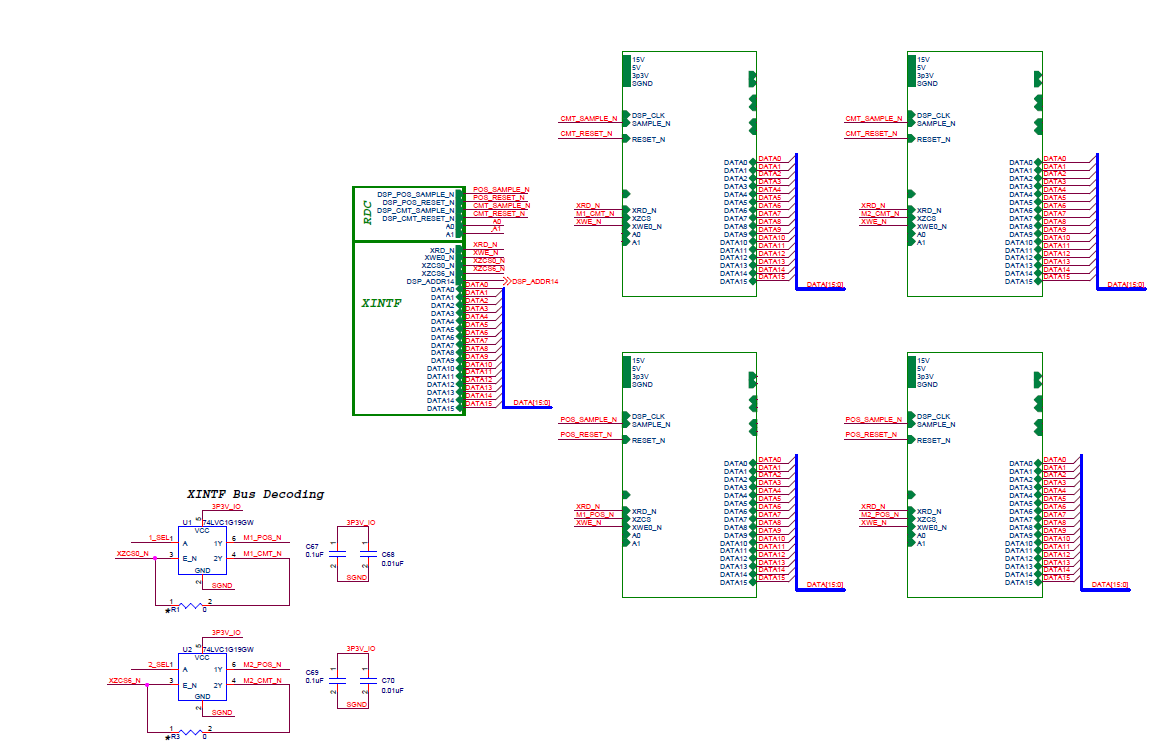

Has anyone tried using a decoder IC to share the parallel bus with multiple devices (sequential access)? I have 2 of the 3 chip selects available and 4 parallel bus devices to interface with. My plan was to put 2 on each of the available zones and use a GPIO as a select for the XCSn pin, decoding via SN74LVC1G19. Pseudo code:

Set_GPIO

ReadRDC1 = *(ZONEn_ADDRESS)

Clear_GPIO

ReadRDC2 = *(ZONEn_ADDRESS)

The decoder will add a delay to the CS edges, but I think that can be compensated for with the lead time parameter, at the cost of a longer overall XINTF acquisition. With XTIMCLK = SYSCLKOUT, I think I can get away with setting XRDLEAD (and XWRLEAD) to 1 (6.67ns) as the decoder has a max propagation delay of 5.4ns. To be safe, I'd probably set it to 2. I also think the delay from de-asserting the chips select should have close to the same effect as putting in a XRDTRAIL value of 1 (i.e. delaying CS wrt to the rest of the bus by 5.4ns).

I would still need to check with setup and hold times on the devices connected to the parallel bus, of course...

Paul