Hi,

I am using the TXS0108e voltage translator to translate logic from 1.8V(from Xilinx FPGA) to 3.3V for a DAC peripheral using SPI interface.

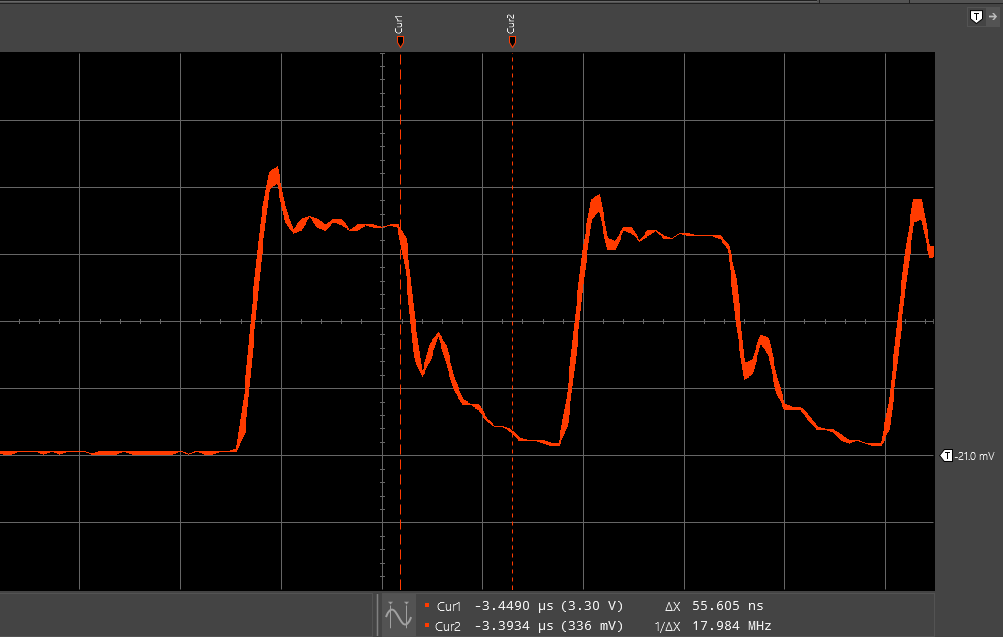

The clock signal after the voltage translator has a slow fall time of around 60ns for a clock of around 6Mhz. While falling the signal starts to rise for some time and then falls again.

What can I do to reduce this fall time?