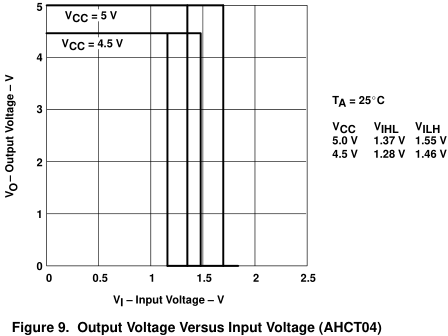

In Logic Guide by TI,attached,5V TTL and 3.3V LVTTL trigger voltage is 1.5V.Can you explain why?And WHY CMOS trigger voltage is 1/2 VCC?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.