Hi team,

My customer has met an issue with CD4094B during power up. Description is as below:

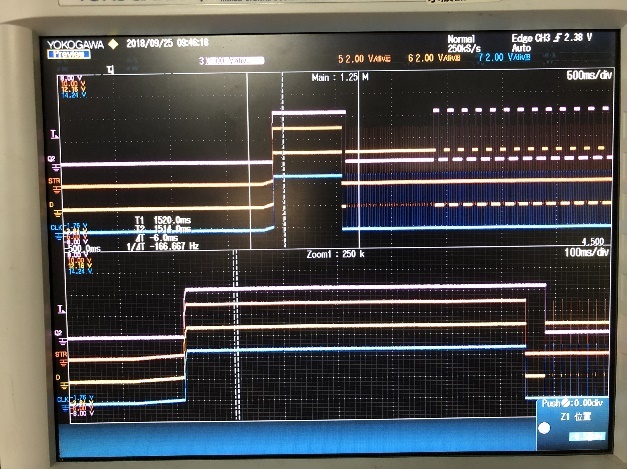

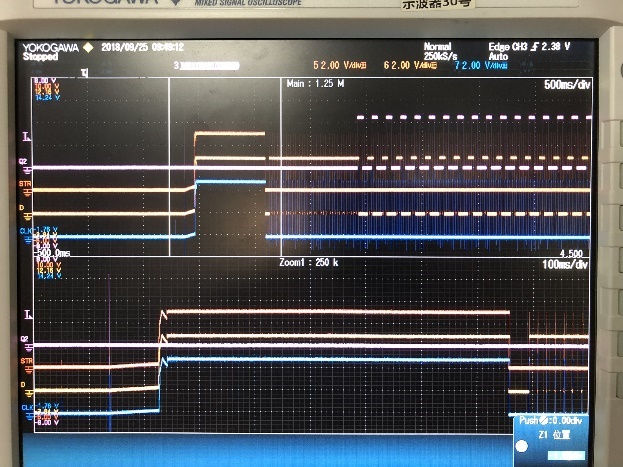

1. CD4094B has control pins of STORBE, DATA, CLOCK, Output enable. All pins are pulled to high during power up.

2. Customer monitors the output Q1~Q7 pin during power up. Some patch of the boards have H-level output while some are L-level output. All the boards have the same design.

Would you help explain if this behavior makes sense and why? Thanks ahead.

Regards

Patrick