Team,

Quick question from my customer:

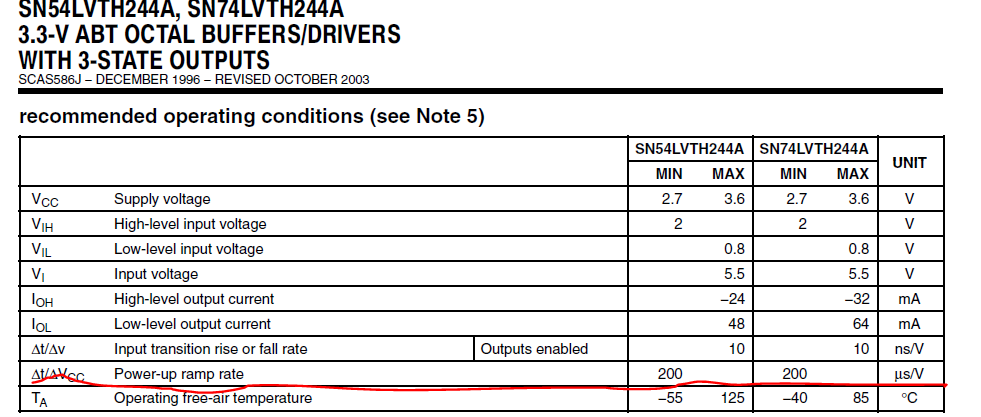

The data sheet for the 54LVTH244A has the following requirements under recommended operation for power supply rise time:

What is the impact to part functionality if the power system does not meet this requirement? We are not using the Ioff and Power-Up 3-State Hot Insertion capabilities of the device in our application.

Thanks for your help