Other Parts Discussed in Thread: SN74LVC1G17, SN74LVC1G14

Hi,

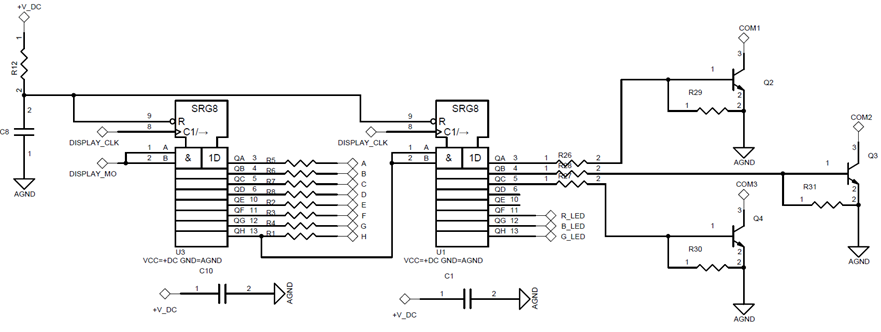

my customer's schematic is as below: U3 and U1 are two SN74HC164.

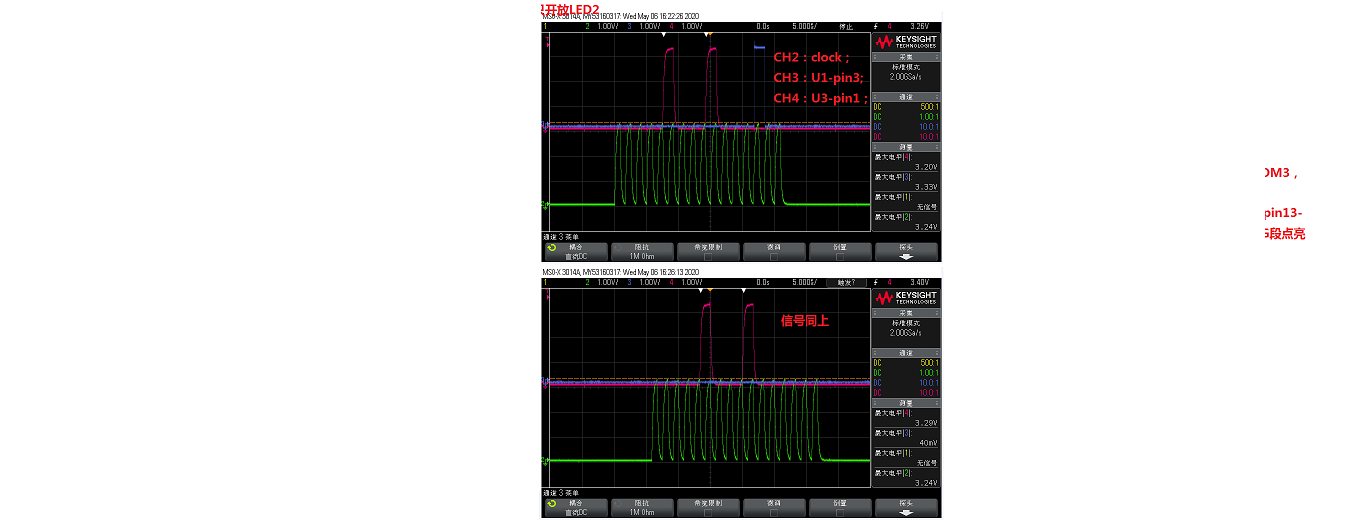

On good board, the waveform is shown below (upper picture). On bad board, the waveform is shown below(lower picture)

CH2-green. U1-PIN3: blue U3-pin1: purple.

In theory, U1-PIN3 should be 9 clocks delayed from U3-PIN1. There should be logic high on blue line after 9clocks of logic high on purple line. But on bad board, the logic high disappear.

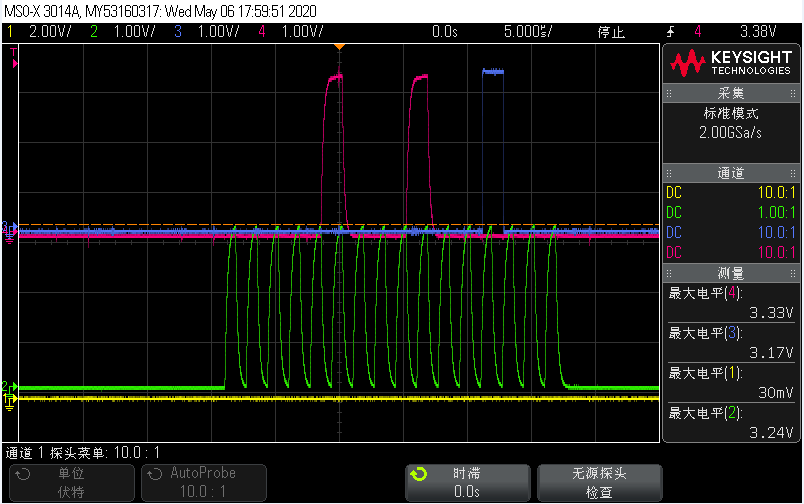

Then we measured the waveform on bad board, but now we measure U1 pin 1 instead of U1 pin3. We can see logic high on U1 pin1 after 8clocks of logic high on U3 pin1.

U1 pin1-blue, U3 pin1- purple

So it shows that the logic high on bad board is skipped from U1 pin1 to U1 pin3.

The problem happens when we use two different batches of SN74HC164 9BATHQK and 9BAECSK. If we use the same batch within 9BATHQK or 9BAECSK, there will be no problem. This device has been used for long in the customer and it's the first time we meet this problem.

Could you please suggest what to do next?