Other Parts Discussed in Thread: SN74AXC2T245, SN74AVC2T244

Hi Sir,

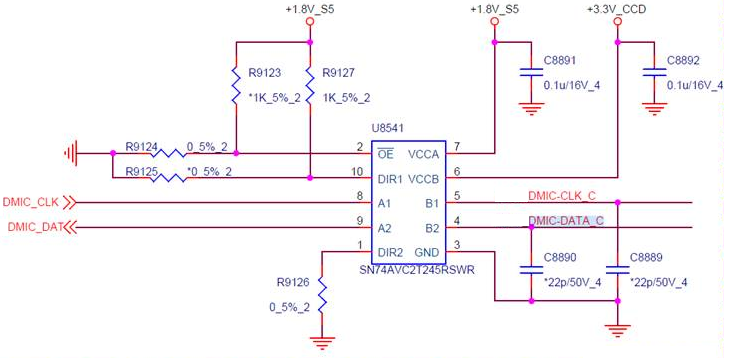

We encountered a weird issue on customer factory they reported they designed SN74AVC2T245 for Dmic level shift 1.8v (PCH) to 3.3v (Dmic module).

But some of DUT not present the proper data from Dmic to PCH, but actually CLK can be delivered to Dmic.

Here are some testing customer did, but not fix:

1. Swap the other brand p2p level shift then works correctly.

2. Re-attach the Dmic module sometimes will become normal.

3. The failure DUT will always encounter the problem.

4. Remove the ESD, EMI solution and any resistors on Dmic PDM DATA/CLK.

Here comes some question would need your support to clarify more:

1. Customer figured out some of DUT will send some noise when boot. They afraid it would cause the problem. What is the V low on input side? If level is low... we should not open the trace and output anything right?

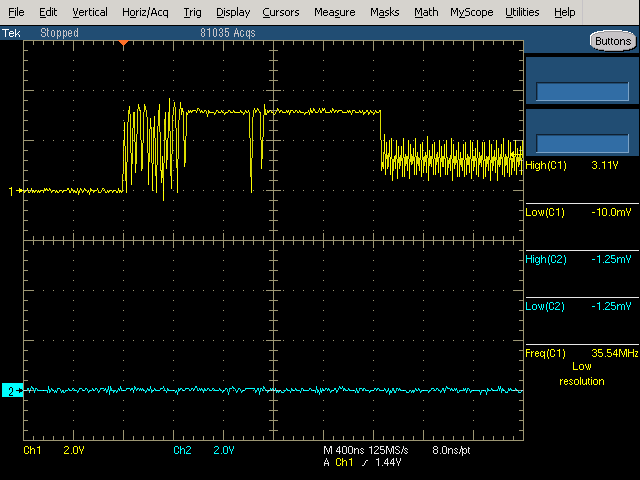

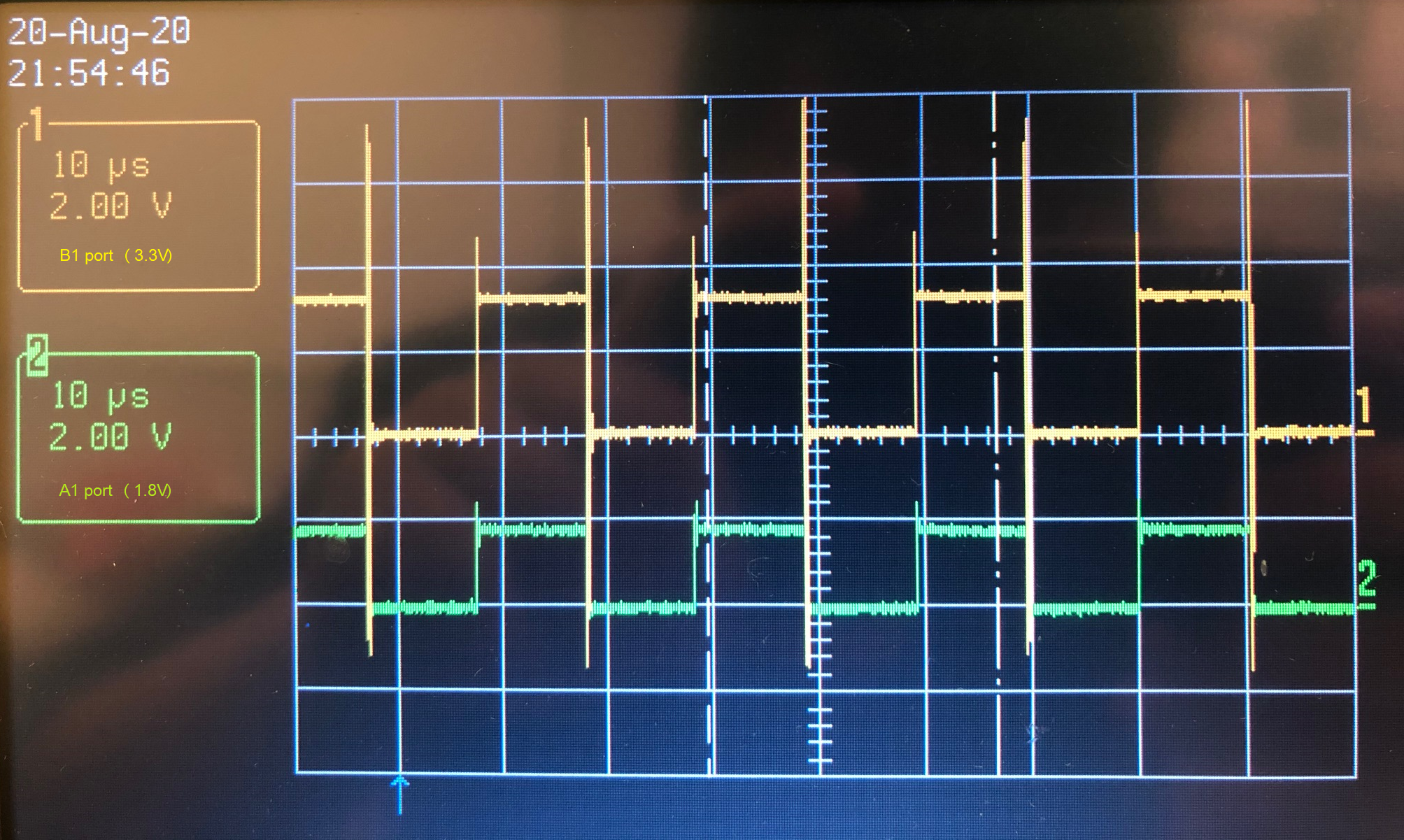

Yellow is B side (3.3v) and Blue is A side (1.8v), meanwhile... 1.8v is low around 0.4v or more lower (this picture not capture with the correct moment)... for the case, the noise should be output?

2. Dmic PDM CLK is working on 2.4MHz... SN74AVC2T245 should not be the problem to handle this clock rate, right?

3. CLK can be delivered properly, but Data is not present out from Dmic... any idea or experience to cause this case?

Looking forward to hearing from you soon, any comments will be appreciated.

Thanks,

George