Other Parts Discussed in Thread: SN74HCS595

Hi Team

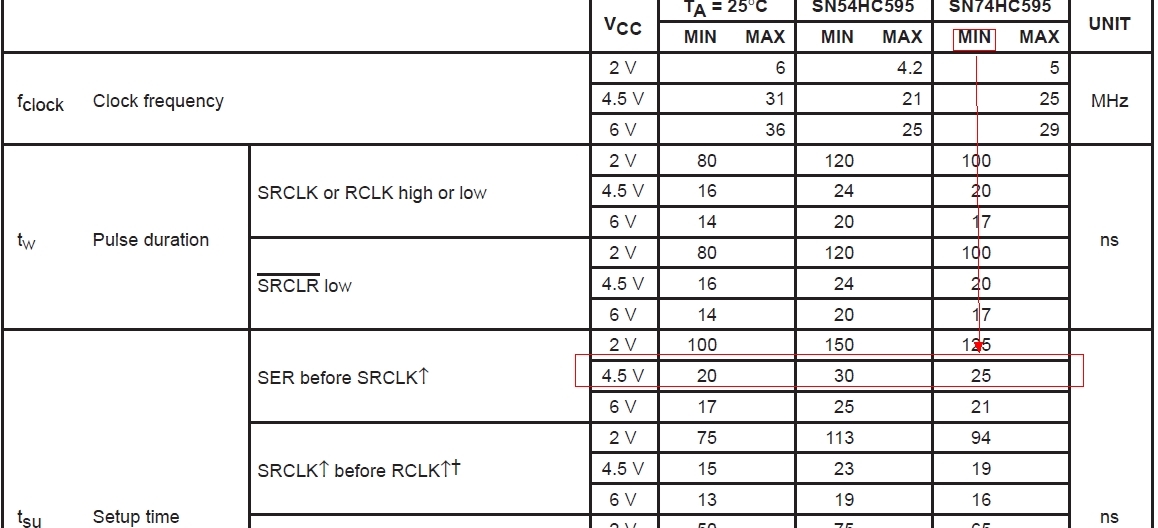

As tables in 7.6 Timing requirements on datasheet shows: The minimum set-up time here is 25ns.

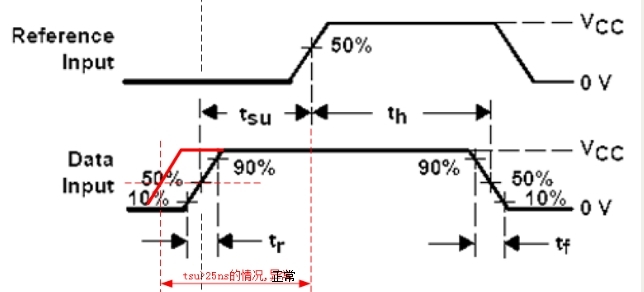

According to logic, if the advance preparation time of stable signal is greater than this time, it can be normally entered into the register (as shown in the figure below, the red signal transmission data SER, the reference signal is SRCLK, and the black mark is Tsu, which is regarded as 25ns

But if the actual signal is not an ideal waveform, that is, the data of the calibration time (marked by the red arrow in the figure above) is not a stable level, will random input level occur?

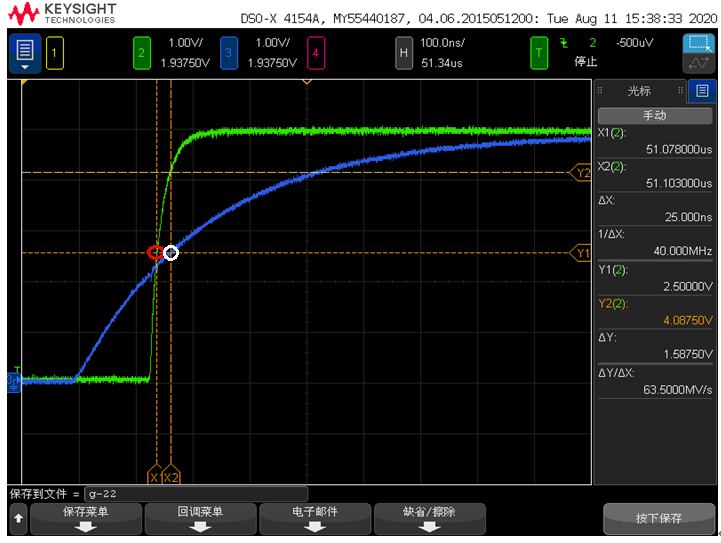

The following is a debug signal waveform (blue is clock, green is data, x1-x2 is 25ns, X2 is 50% of clock). What is the data input into the chip? Is the input level at 50% of the point or at other time points (the level is not stable)