Hi,

I want to define the dynamic power consumption of a translator (SN74LVC8T245).

My 8 channel translator is used with the below characteristics to interface a 2,5V FPGA bank with a 3,3V memory. :

Vcca=2,5V

Vccb=3,3V

f=1MHz (8 outputs switching)

CL=8pF (memory input capacitance per channel)

According to SN74LVC8T245 datasheet Cpd=2pF.

Applying formula described in "CMOS Power Consumption and Cpd Calculation, literature number SCAA035", I get :

> For Transient power consumption :

PT = Cpd x VCC² x fI x NSW = 2pF x 2,5² x 1MHz x 8 = 0,1mW ie IT = 0,25mA

> For Capacitive-Load Power Consumption is :

PL = CL x VCC² x fo x NSW (CL is the load per output) = 8pF x 3,3² x 1MHz x 8 = 0,69mW ie IL = 0,21mA

Looking at doc SCAA035 :

--> Figure 8 (Power Consumption With a Single Output Switching around) indicates dynamic current around 1mA@1MHz

--> Figure 7 (Power Consumption With All Outputs Switching) indicates dynamic current around 25mA@1MHz

1) power consumption for 8 output switching (Figure 7) is quite different from 8x power consumption for 1 output switching (Figure 8) --> Any explication ?

2) power calculation @1mHz is for IT is very different from Figure 7 data (ratio=100) --> something must be wrong in calculation ?

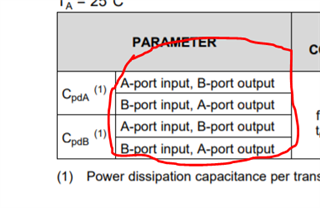

3) In SN74LVC8T245 datasheet, what is the difference between Cpda and Cpdb ? Which value should I consider ?

Thanks for any precision.

Baptiste