Hi Team

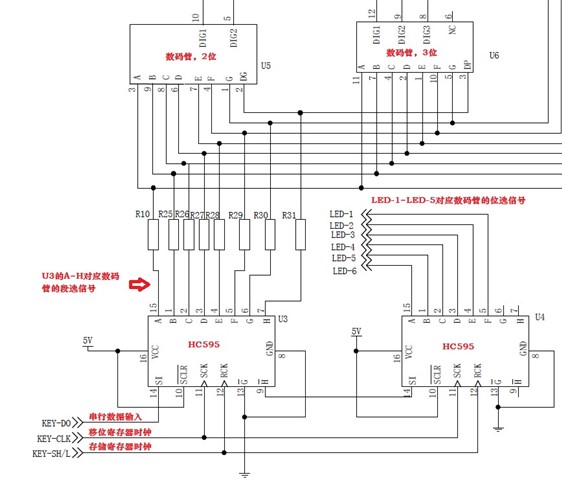

when degugging SN74HC595, cascade connection, the secord part has some randomly error in some bit. I am suspecting the QH' and SRCLK,

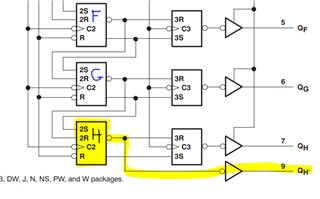

The rising edge of the 9th SCRLK will send the QH' pin value (@8th SCRLK) to the second part SER pin, meanwhile it will update the first sn74hc595

QH 'pin value. If QH' update earlier than the QH' sent to second part SER input, then the second part would be error.

Am i understanding right? Is the QH' falling edge would be later than 9th SRCLK rising? Is there any way or hint for me to measure and test to make it more clarified to show what parameter?