Hi Team,

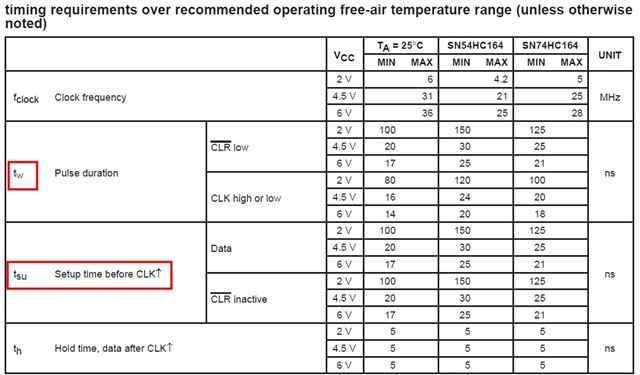

I would like to know what the mean of the tsu.

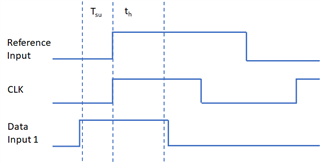

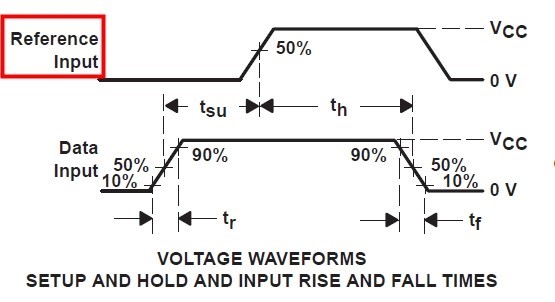

I read the data sheet, it says "set up time before CLK", but in the picture, I didn't understand the meaning of the picture.

- What does reference input refer to?

- Why does tsu start with the rise of data input and end with the rise of Reference?

- What does tsu show?

Thanks for your help in advance!

BR

Jenson