Other Parts Discussed in Thread: SN74LVC3G17, SN74LVC1G97, SN74LVC1G99, SN74LVC1G123

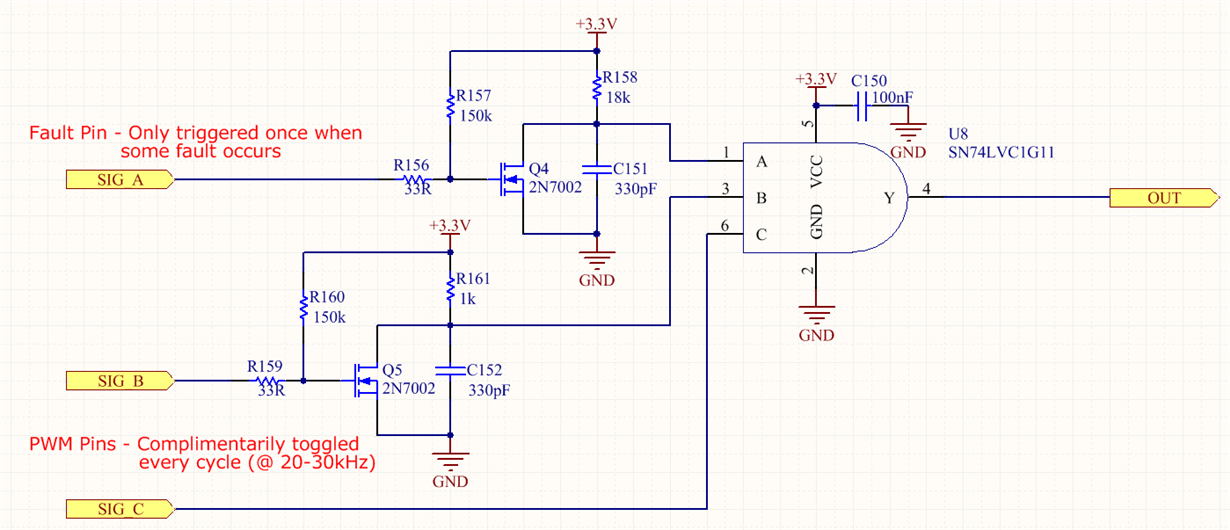

I have an application where I need to use discrete logic to control the input to a driver IC. Some of the key criteria included using only one IC in a small package and relatively low propagation delay. I chose to use the SN74LVC1G11(Single 3-Input Positive-AND Gate) to accomplish the task.

See attached simulation/schematic.

There is very specific behaviour that is required from this circuit, including some inversion and latching (for a period of time) of input signals. The circuit does exactly what I need but after I had built the first prototype, I have discovered some possible design issues (Note: Not from testing but from datasheet analysis).

I believe that both RC delay circuits on inputs A and B violate the "Δt/Δv Input transition" rating of 10ns/V. If I understand correctly with a VCC of 3.3VDC, to comply with the datasheet figures, I need to ensure the inputs transition within about 33ns from 0.8V to 2V. Is that understanding correct?

Signal B and C are toggled at 20kHz. Signal A is rarely toggled - It's a fault pin that is meant to send the output low if signal A goes high. It's designed to latch the output of the gate low for a few microsecs (kind of one shot behaviour).

Signal input C is ok - no violation. Signal B input stays between 0.8V - 2V for about 200ns while Signal A stays in transistion for several micoseconds.

Does this situation pose any real risk? I don't believe there will be any significant increase in VCC current nor will there be any additional heating. I haven't witnessed any oscilliations in testing either. I have read the app note regarding slow inputs but the paper emphasizes the risk when there are multiple gates in a single package. In this case there is only one gate and for my analysis the risk seems quite minute.

If I had to change this part, I suppose I should use a part with schmitt trigger inputs. I can't find any single 3 input AND gate with schmitt trigger inputs nor even a dual AND gate that I could cascade. Are there any other options, noting that I need single gate IC solution and prefer a low total propagation delay.

Thanks