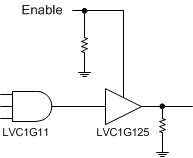

Other Parts Discussed in Thread: SN74LVC1G125

Hi,

can it be guaranteed that the output (Y) stays low while power-up (if at least 1 input is at 0V)? Or does one have to expect that the output "shifts/moves" until minimal supply voltage is reached?

Thank you,

Andreas