Other Parts Discussed in Thread: TXB0104

There is serious reflection showed as attached picture when sending 2MHz clock from TXB0304UTR to xilinx XC3S400AN CPLD through 180mm trace. Tried below experiment but cannot fix the problem:

- Add serial resistor (10,20,30,50,100 ohm) close to TXB0304

- Add 10pF+100pF+47pF capacitors near TXB0304 VCC

- Add 10pF,100pF,47pF parallel capacitor between CLK to GND close to CPLD

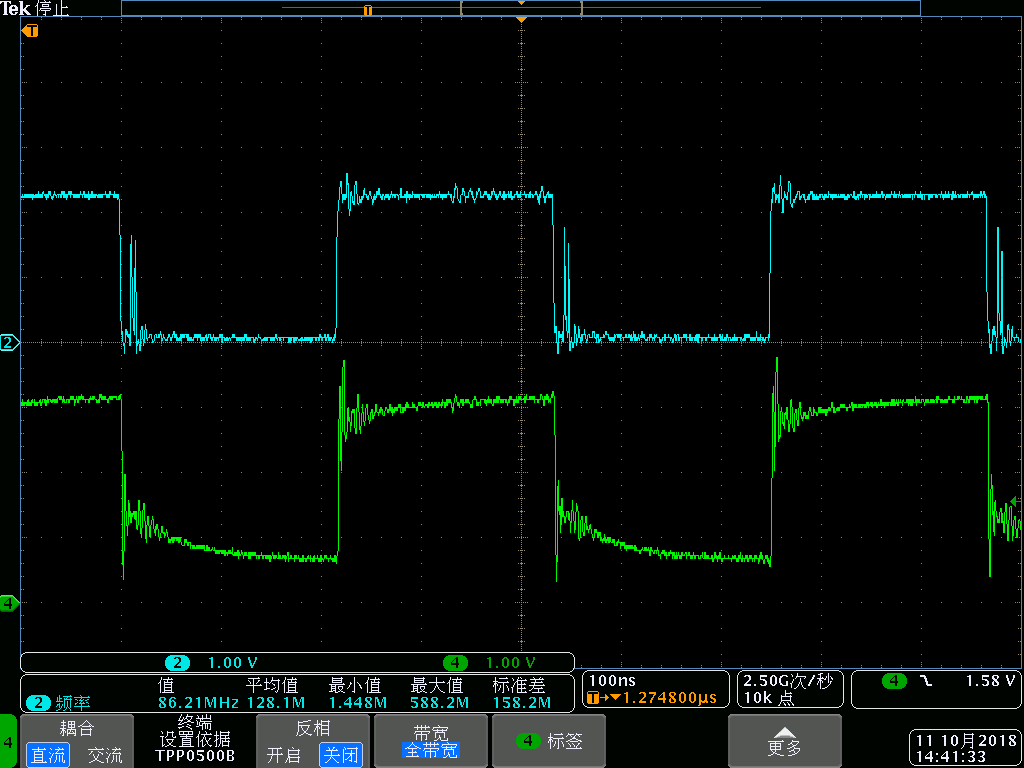

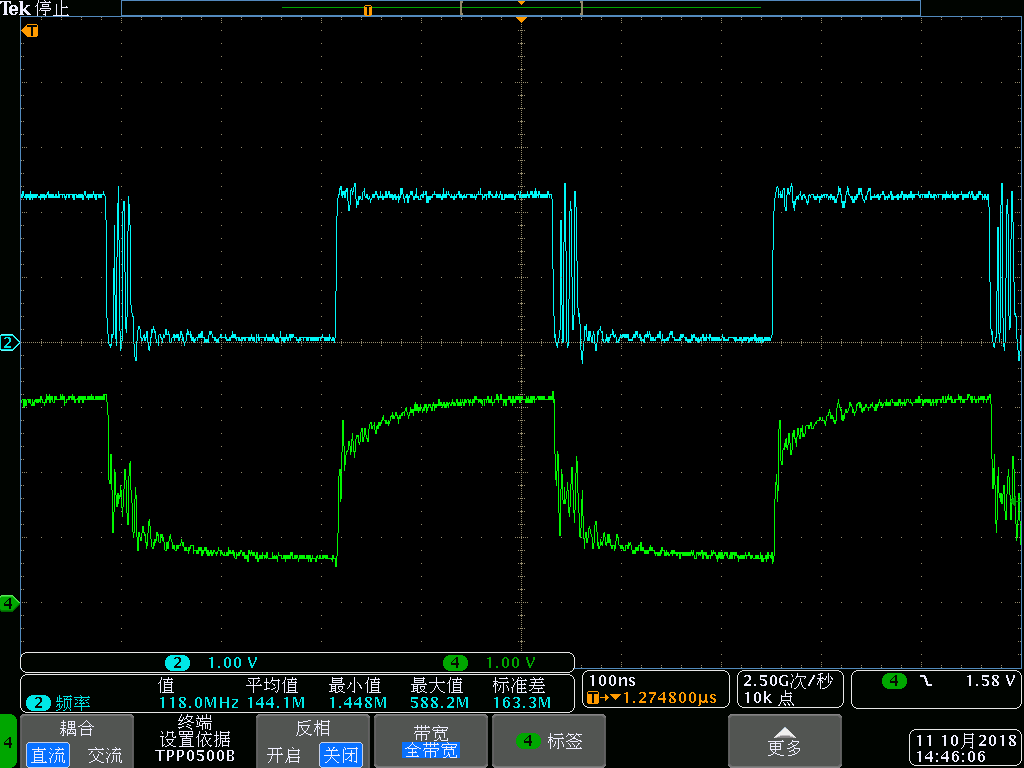

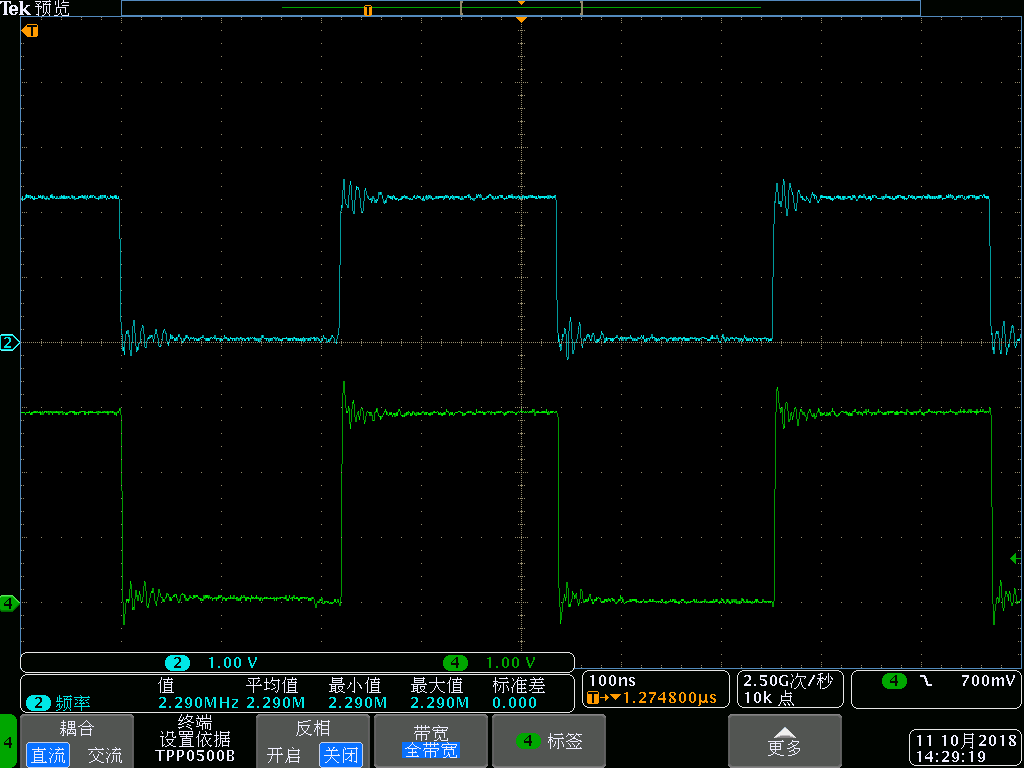

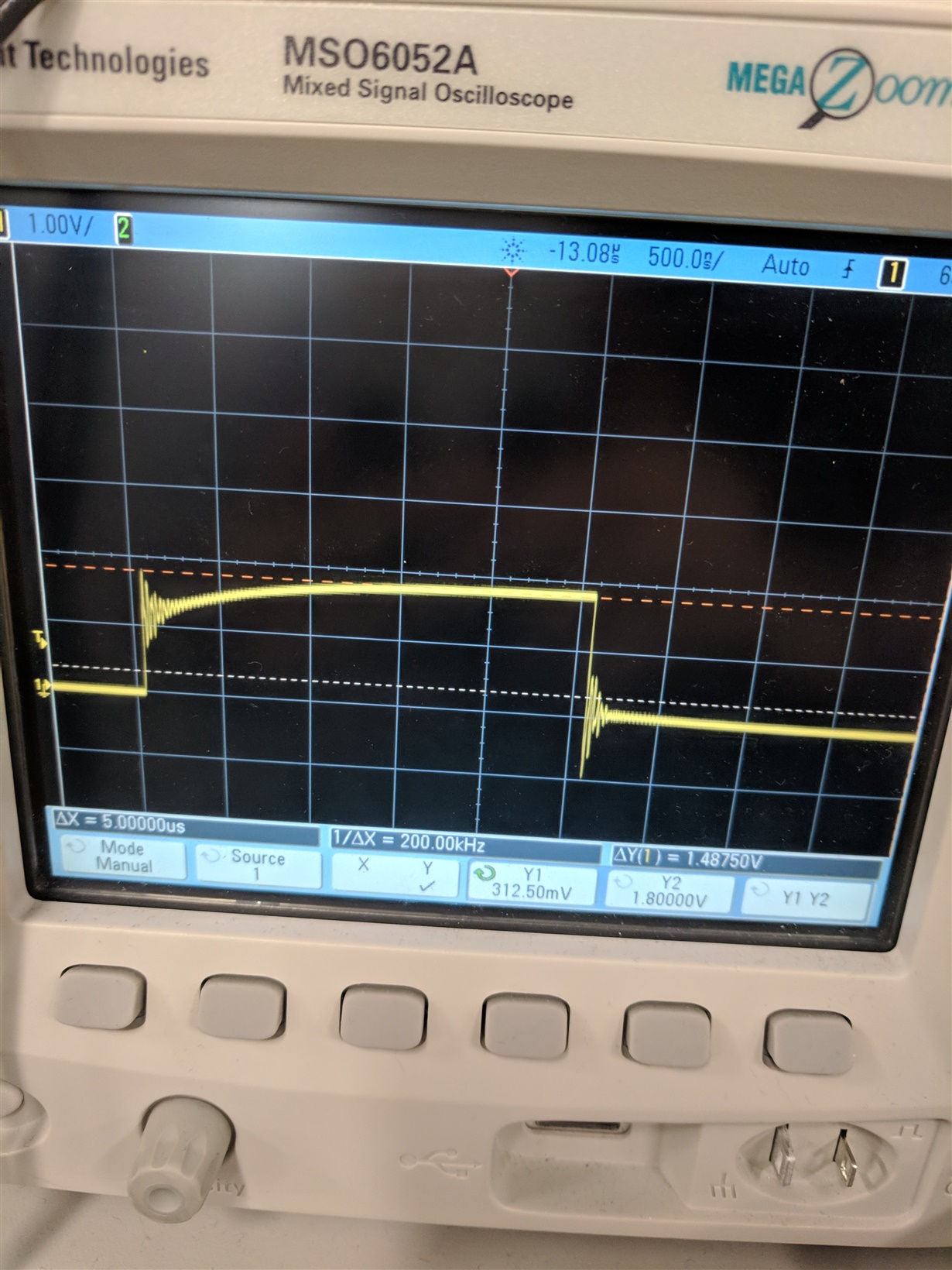

In the figure, blue wave is the input signal and green wave is the output signal.

figure a, serial resistor vlaue=0Ω

figure b, serial resistor vlaue=50Ω

figure c, serial resistor vlaue=150Ω

figure d, serial resistor not Weld