Other Parts Discussed in Thread: SN74LVC07A, SN74AUC125, SN74LVC2G125

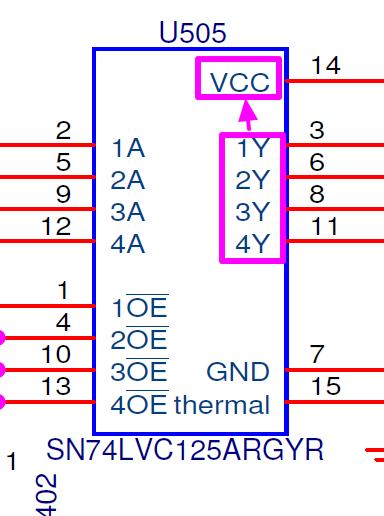

Now we found a voltage leak problem on the SN74LVC125A buffer, and the voltage will leak from the output to the Vcc, voltage delta is about 0.5V, and it will happen on no matter the output enable or disable.

We found that this problem has nothing to do with our peripheral circuits, only this buffer. Pls help check this.