Other Parts Discussed in Thread: SN74AUC1G17

Hi team,

My customer is using our SN74LVC1G17 level shift to drive 12 channel SDI IC.

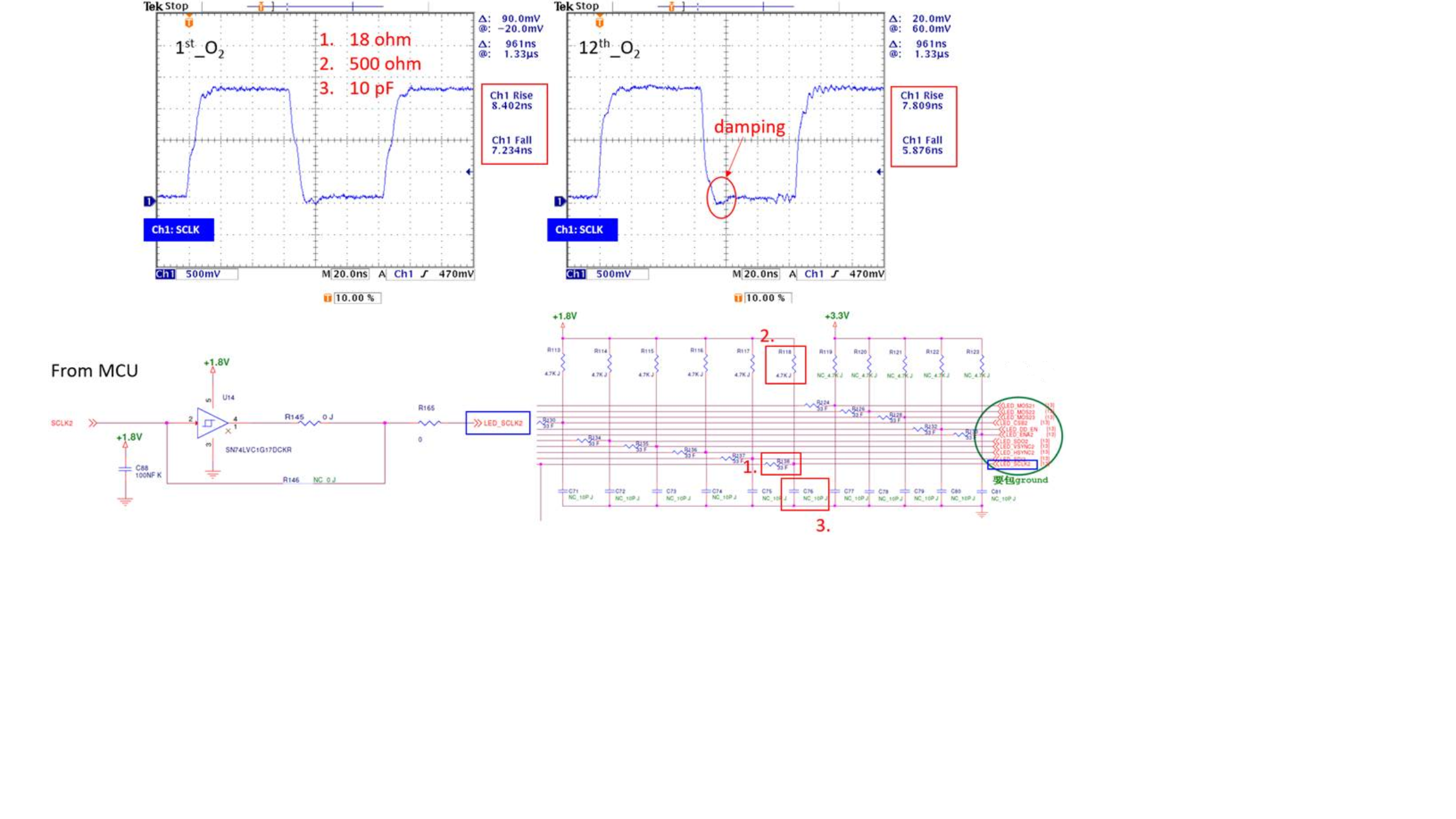

The schematic and the output waveform is as below.

They have used two kind of situation. The difference of them is using different condition of open drain resistor (2), series resistor (1) and parallel cap (3) in the schematic.

First one: 1. series resistor=18ohm, 2. open drain resistor=500 ohm, 3. parallel capacitor=10pF

Result: Worst rising time in 12 channel=8.402 ns

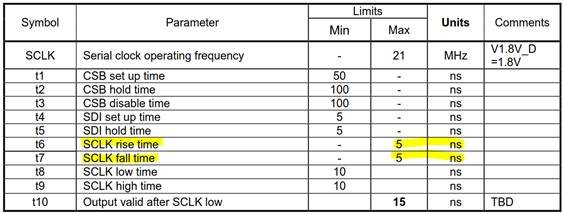

It is not allowed by next stage IC. The spec is only 5ns

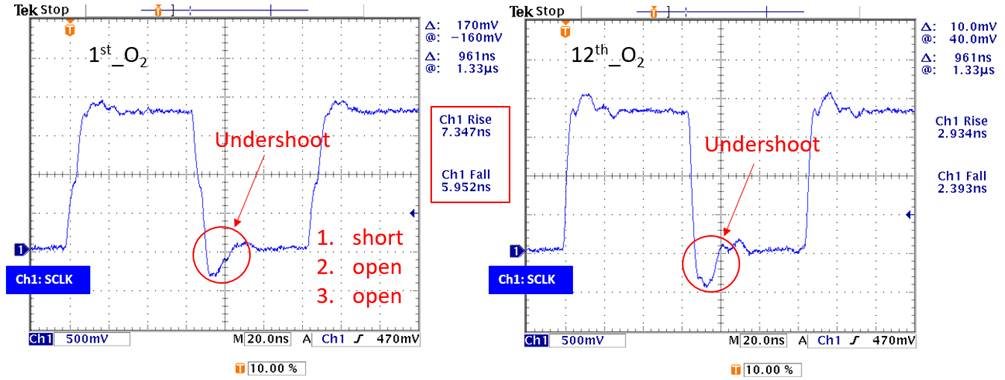

Second one: 1. series resistor=short, 2. open drain resistor=open, 3. parallel capacitor=open

Result: rising time has improved but it will have undershoot behavior

May I have your help? How to improve the undershoot behavior ? Is it the measurement error or not? The input capacitance of probe is about 8pF. The trace between level shift to SDI IC is about 8000mil.