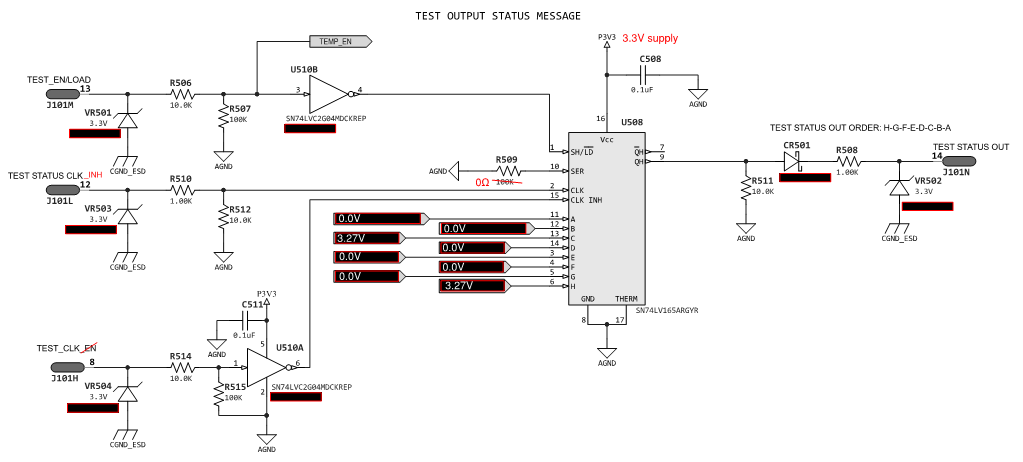

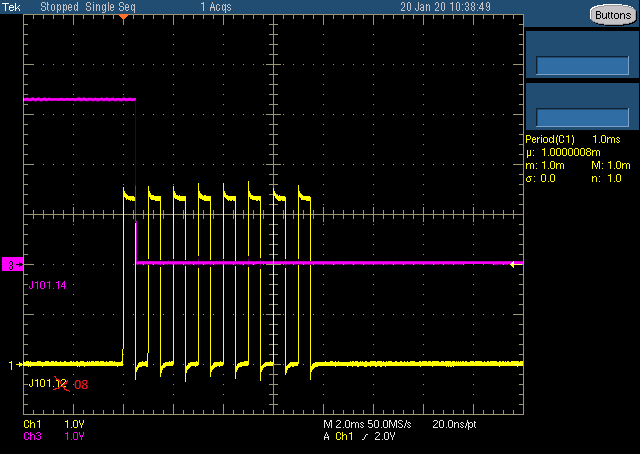

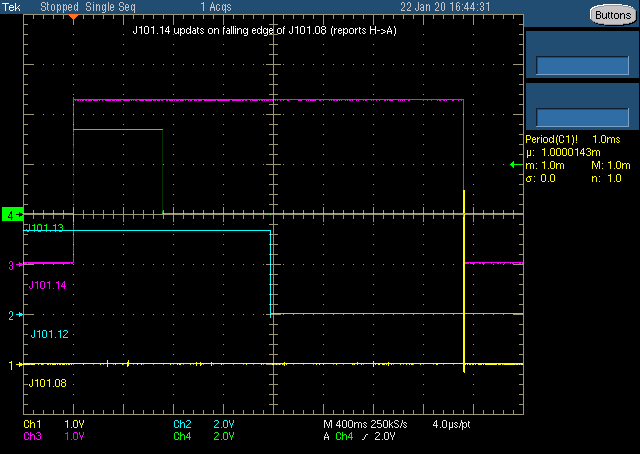

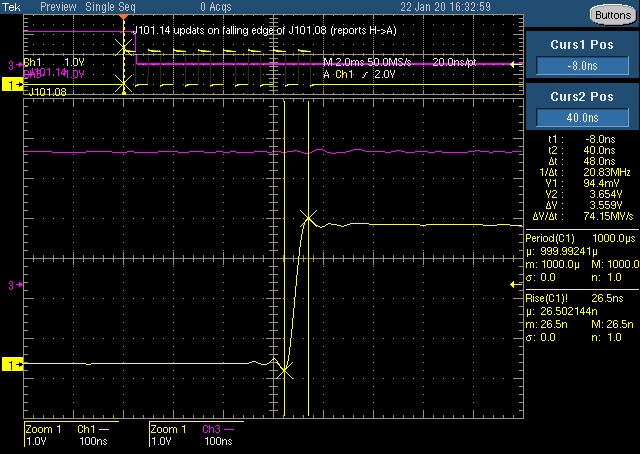

I'm using the SN74LV165A in one of my prototype designs and cannot get the Q_H or \Q_H output to change states. The Q_H remains LOW while the \Q_H remains HIGH. Two of my parallel inputs are set HIGH with the rest LOW for this scenario, and SER is pulled LOW as well. I've sent the \LD pin LOW for ~1sec then send my 8 clock pulses (1ms 50% duty cycle) to the CLK pin (while CLK_INH set Low). But the outputs do not change states and instead remain static. I've tried this on 3 devices so far with the same results. The only thing I can think of is that the Low SER input is somehow overriding the parrallel H-A inputs, but I dont see anything in the datasheet related to such a thing (other than the first page wherein \LD held Low is independent of CLK, CLK_INH, & SER states).

The first time after power-up that I send the \LD pulse, the Q_H goes from Low to High. Then when the CLK pulses are sent, the Q_H goes from High to Low and stays there. I have tried various clock pulse widths with no impact to output.

Any insight on why the outputs would not be changing would be greatly appreciated.