Other Parts Discussed in Thread: SN74LV221A

I have a puzzling case of a not so rare failure of the SN74LVC1G123DCTR part in production.

I am seeing occasional (perhaps 1 in 500) failures of the SN74LVC1G123DCTR to function correctly.

The failure mode is perplexing too, in that it may fail to function at room temperature, but will begin functioning correctly at elevated temperature, or may function correctly at room temperature, but will fail to function correctly at a slightly lower temperature.

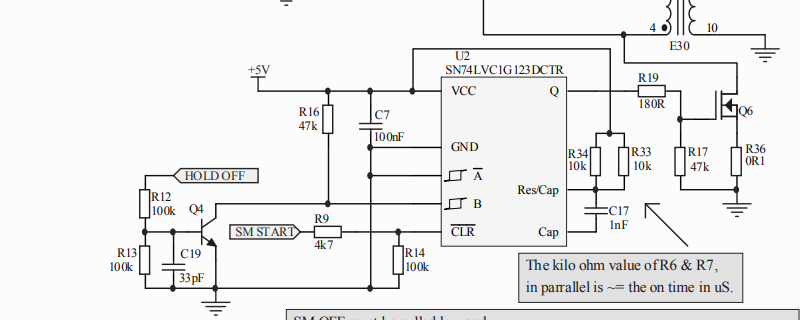

I have included my schematic around the SN74LVC1G123DCTR, which I have designed to pulse a MOSFET on for a fixed period in an oscillator flyback voltage boost design.

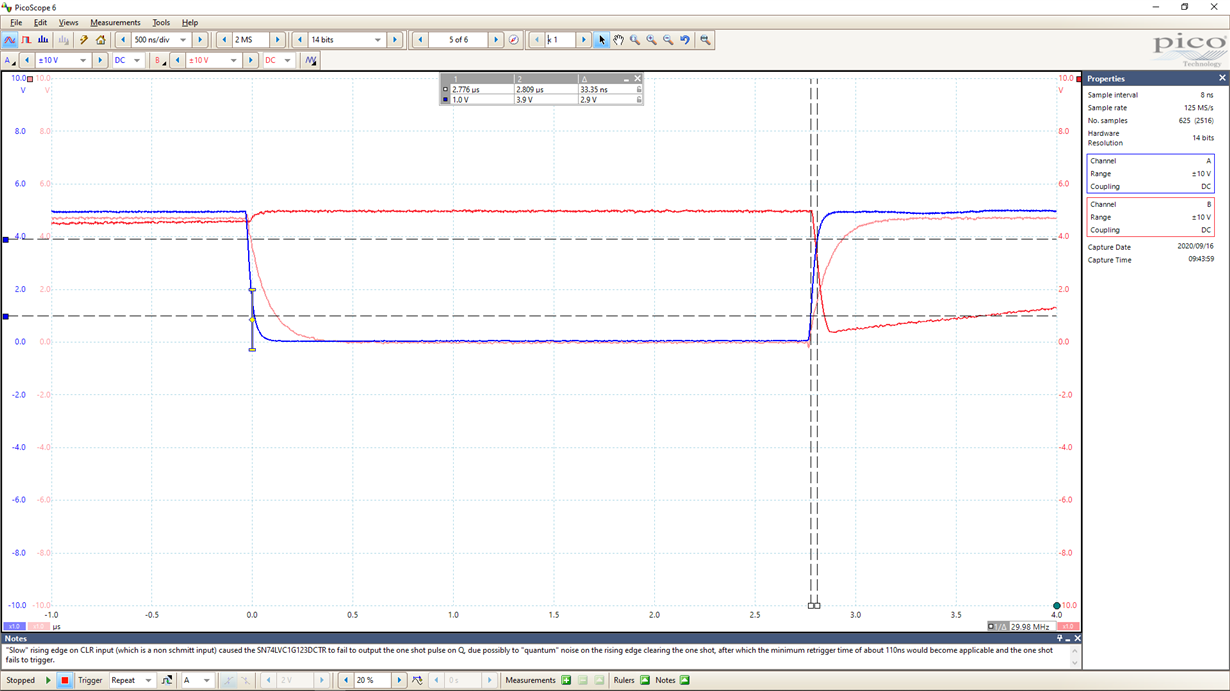

The failure mode is that the output Q, simply does not go to logic high for the one shot period as one would expect under the following condition;

With input A(BAR) bonded to circuit 0V, input B pulled up with 47k and CLR(BAR) initially held low (tied to an MCU IO pin).

When the CLR input is taken high and held high, no one shot pulse appears on the Q output.

The MCU firmware then continues to pulse the CLR input, low for 5uS and high for 2ms on an ongoing basses attempting to start the oscillator (flyback) process.

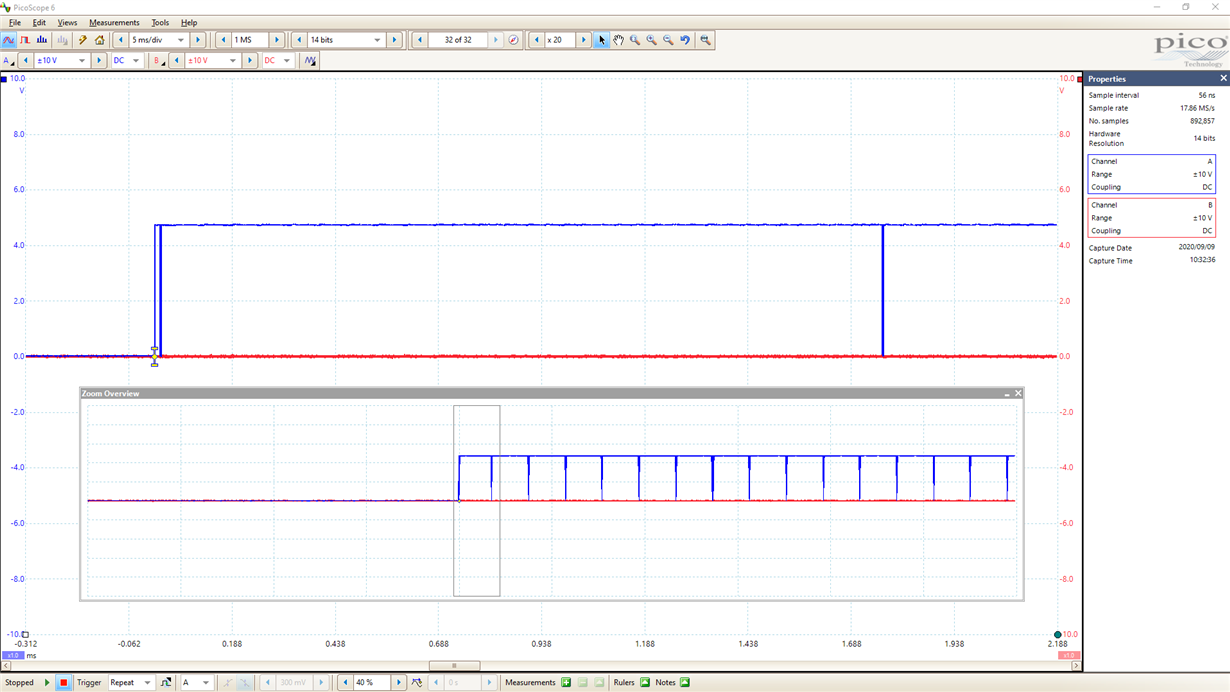

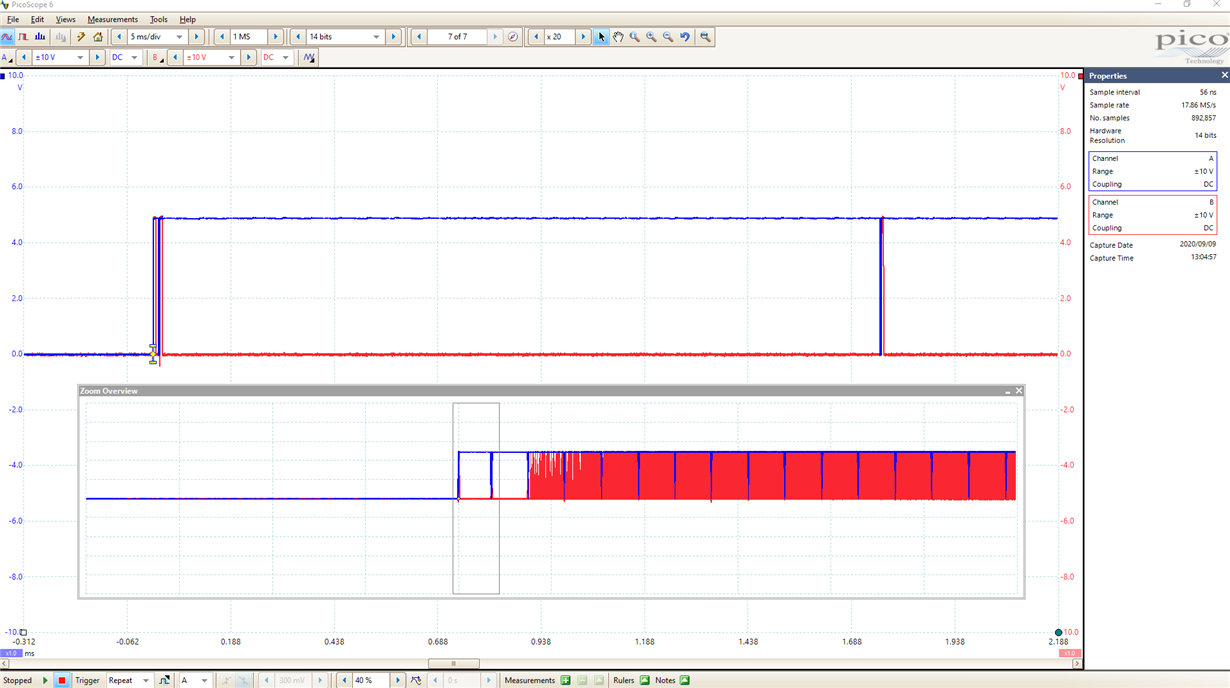

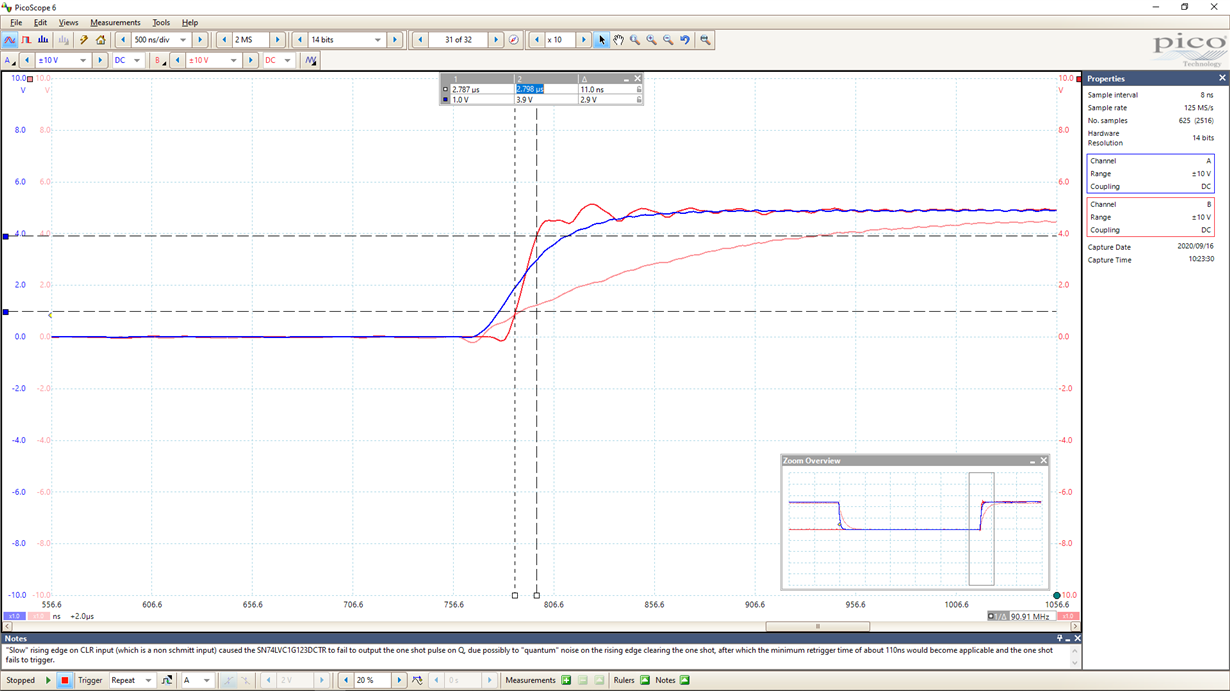

I have included 2x scope screenshots.

Ch-A the blue trace, probe is on the CLR input.

Ch-B the red trace, probe is on the Q output.

The "TI fail to OSC" file shows that the one shot is not raising the Q output to high at room temperature and the "TI osc at temperature" shows the same capture and circuit functioning when heated with a hot air pencil.

I have seen this type of fault once previously in my many decades old career as a development engineer.

The cause back then on that occasion was due to a bond out wire going open circuit when the SMT package cracked during IR soldering due to moisture ingress into the SMT parts in stock.

The SN74LVC1G123DCTR part seems to not indicate any moisture sensitivity in the data sheet or packaging though?

I appreciate any feedback on this issue.