Other Parts Discussed in Thread: SN74AXC8T245, SN74AXCH8T245

Dear Sir,

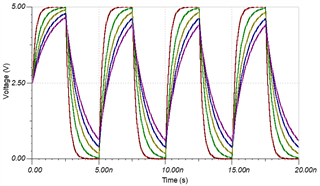

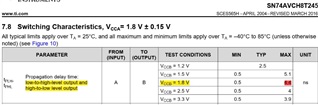

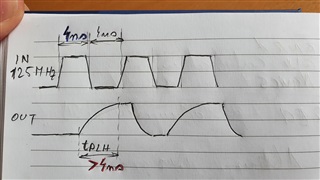

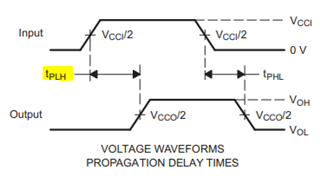

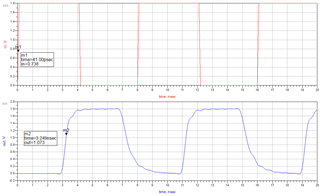

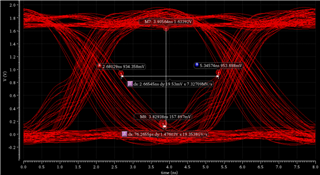

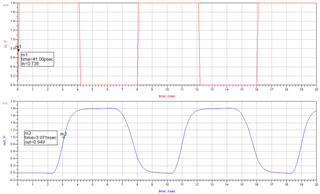

Have you an explanation regarding huge propagation delay dispersion from 0.5 ns which is minimum up to 4.4 ns which is maximum? for SN74AVCH8T245 device.

Considering maximum propagation delay, this device doesn't meet 320 Mbps data rate, instead it can be around 55 Mbps.

Thank you,

Nicolae Zaharia.