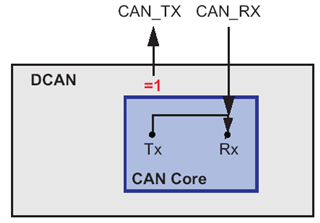

Hello, we are working on DCAN implementation in the LAUNCHXL2-RM46. We tested the Loopback mode and the LoopBack Combined with Silent Mode properly (Attached I send the signal seen from the Tx Port). However, the implementation of silent mode test and not test mode by the connection between Tx and Rx are not working. It seems that the Rx pin is not connected to the peripheral because when using it, we have not seen any type of information in the RAM either signal on the signal analyzer. We tested these configurations with DCAN1 and DCAN2 (canInit function attached here) and we obtained the same response.

.

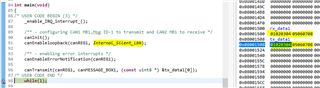

. void canInit(void)

{

/* USER CODE BEGIN (4) */

/* USER CODE END */

/** @b Initialize @b CAN1: */

/** - Setup control register

* - Disable automatic wakeup on bus activity

* - Local power down mode disabled

* - Disable DMA request lines

* - Enable global Interrupt Line 0 and 1

* - Disable debug mode

* - Release from software reset

* - Enable/Disable parity or ECC

* - Enable/Disable auto bus on timer

* - Setup message completion before entering debug state

* - Setup normal operation mode

* - Request write access to the configuration registers

* - Setup automatic retransmission of messages

* - Disable error interrupts

* - Disable status interrupts

* - Enter initialization mode

*/

canREG1->CTL = (uint32)0x00000200U

| (uint32)0x00000000U

| (uint32)((uint32)0x00000005U << 10U)

| (uint32)0x00020043U;

/** - Clear all pending error flags and reset current status */

canREG1->ES |= 0xFFFFFFFFU;

/** - Assign interrupt level for messages */

canREG1->INTMUXx[0U] = (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U;

canREG1->INTMUXx[1U] = (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U

| (uint32)0x00000000U;

/** - Setup auto bus on timer period */

canREG1->ABOTR = (uint32)4U;

/** - Initialize message 1

* - Wait until IF1 is ready for use

* - Set message mask

* - Set message control word

* - Set message arbitration

* - Set IF1 control byte

* - Set IF1 message number

*/

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Potentially infinite loop found - Hardware Status check for execution sequence" */

while ((canREG1->IF1STAT & 0x80U) ==0x80U)

{

} /* Wait */

canREG1->IF1MSK = 0xC0000000U | (uint32)((uint32)((uint32)0x1FFFFFFFU & (uint32)0x1FFFFFFFU) << (uint32)0U);

canREG1->IF1ARB = (uint32)0x80000000U | (uint32)0x40000000U | (uint32)0x20000000U | (uint32)((uint32)((uint32)0x00000801U & (uint32)0x1FFFFFFFU) << (uint32)0U);

canREG1->IF1MCTL = 0x00001000U | (uint32)0x00000800U | (uint32)0x00000000U | (uint32)0x00000000U | (uint32)6U;

canREG1->IF1CMD = (uint8) 0xF8U;

canREG1->IF1NO = 1U;

/** - Initialize message 2

* - Wait until IF2 is ready for use

* - Set message mask

* - Set message control word

* - Set message arbitration

* - Set IF2 control byte

* - Set IF2 message number

*/

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Potentially infinite loop found - Hardware Status check for execution sequence" */

while ((canREG1->IF2STAT & 0x80U) ==0x80U)

{

} /* Wait */

canREG1->IF2MSK = 0xC0000000U | (uint32)((uint32)((uint32)0x1FFFFFFFU & (uint32)0x1FFFFFFFU) << (uint32)0U);

canREG1->IF2ARB = (uint32)0x80000000U | (uint32)0x40000000U | (uint32)0x00000000U | (uint32)((uint32)((uint32)0x00000801U & (uint32)0x1FFFFFFFU) << (uint32)0U);

canREG1->IF2MCTL = 0x00001000U | (uint32)0x00000400U | (uint32)0x00000000U | (uint32)0x00000000U | (uint32)6U;

canREG1->IF2CMD = (uint8) 0xF8U;

canREG1->IF2NO = 2U;

/** - Setup IF1 for data transmission

* - Wait until IF1 is ready for use

* - Set IF1 control byte

*/

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Potentially infinite loop found - Hardware Status check for execution sequence" */

while ((canREG1->IF1STAT & 0x80U) ==0x80U)

{

} /* Wait */

canREG1->IF1CMD = 0x87U;

/** - Setup IF2 for reading data

* - Wait until IF1 is ready for use

* - Set IF1 control byte

*/

/*SAFETYMCUSW 28 D MR:NA <APPROVED> "Potentially infinite loop found - Hardware Status check for execution sequence" */

while ((canREG1->IF2STAT & 0x80U) ==0x80U)

{

} /* Wait */

canREG1->IF2CMD = 0x17U;

/** - Setup bit timing

* - Setup baud rate prescaler extension

* - Setup TSeg2

* - Setup TSeg1

* - Setup sample jump width

* - Setup baud rate prescaler

*/

canREG1->BTR = (uint32)((uint32)0U << 16U) |

(uint32)((uint32)(6U - 1U) << 12U) |

(uint32)((uint32)((3U + 6U) - 1U) << 8U) |

(uint32)((uint32)(4U - 1U) << 6U) |

(uint32)19U;

/** - CAN1 Port output values */

canREG1->TIOC = (uint32)((uint32)1U << 18U )

| (uint32)((uint32)0U << 17U )

| (uint32)((uint32)0U << 16U )

| (uint32)((uint32)1U << 3U )

| (uint32)((uint32)1U << 2U )

| (uint32)((uint32)1U << 1U );

canREG1->RIOC = (uint32)((uint32)1U << 18U )

| (uint32)((uint32)0U << 17U )

| (uint32)((uint32)0U << 16U )

| (uint32)((uint32)1U << 3U )

| (uint32)((uint32)0U << 2U )

| (uint32)((uint32)0U <<1U );

/** - Leave configuration and initialization mode */

canREG1->CTL &= ~(uint32)(0x00000041U);

}

Thanks for your support.

Daniel