Other Parts Discussed in Thread: AM2434, SYSCONFIG

Hi,

we are working on our custom board with AM2434 an LPDDR4 assembled.

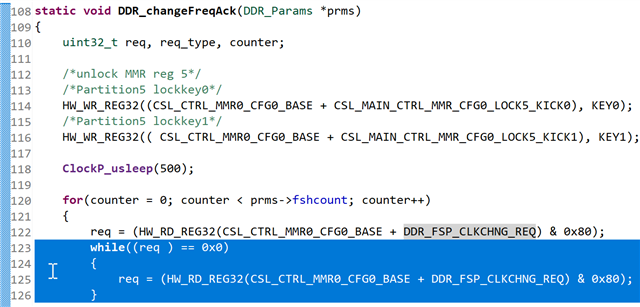

During the initialisation of the LPDDR4, I run into a dead loop at line 123 in DDR_changeFreqAck() in ddr.c. Please refere to the picture below.

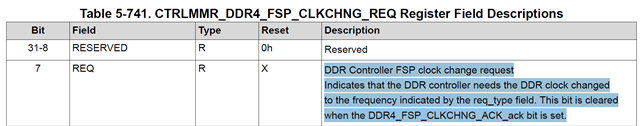

The loop waits untill Bit 7 of CTRLMMR_DDR4_FSP_CLKCHNG_REQ Register is non zero. Which only gets cleard by DDR4_FSP_CLKCHNG_ACK Register

Where does Bit 7 of CTRLMMR_DDR4_FSP_CLKCHNG_REQ get set during the initialisation?

From DDR_setFreq() I do not get an error message.

Greetings

Tom