Other Parts Discussed in Thread: SYSCONFIG

Hi!

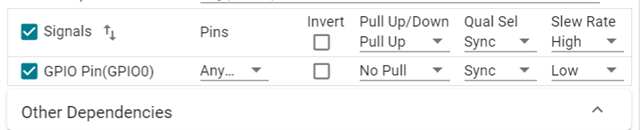

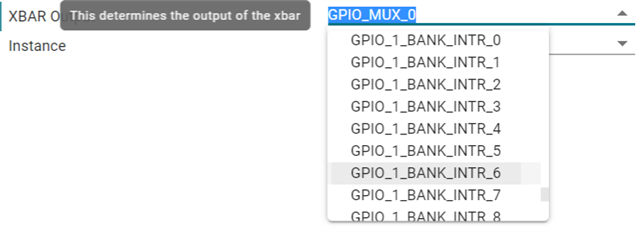

using AM263x I want to set Qualifier to a bank of GPIO's.

Is there a table that list the GPIO's according to their bank/group ?

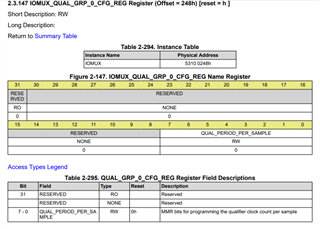

I see in the TRM that there are 16pins per bank, and there are 9 banks per module...

Thanks

Carmel